Table - table 1-38: parameters, Heading3 - verilog instantiation template, Verilog instantiation template – Achronix Speedster22i User Macro Guide User Manual

Page 50

I/O Cells

OPAD_D2

Speedster Macro Cell Library

PAGE 33

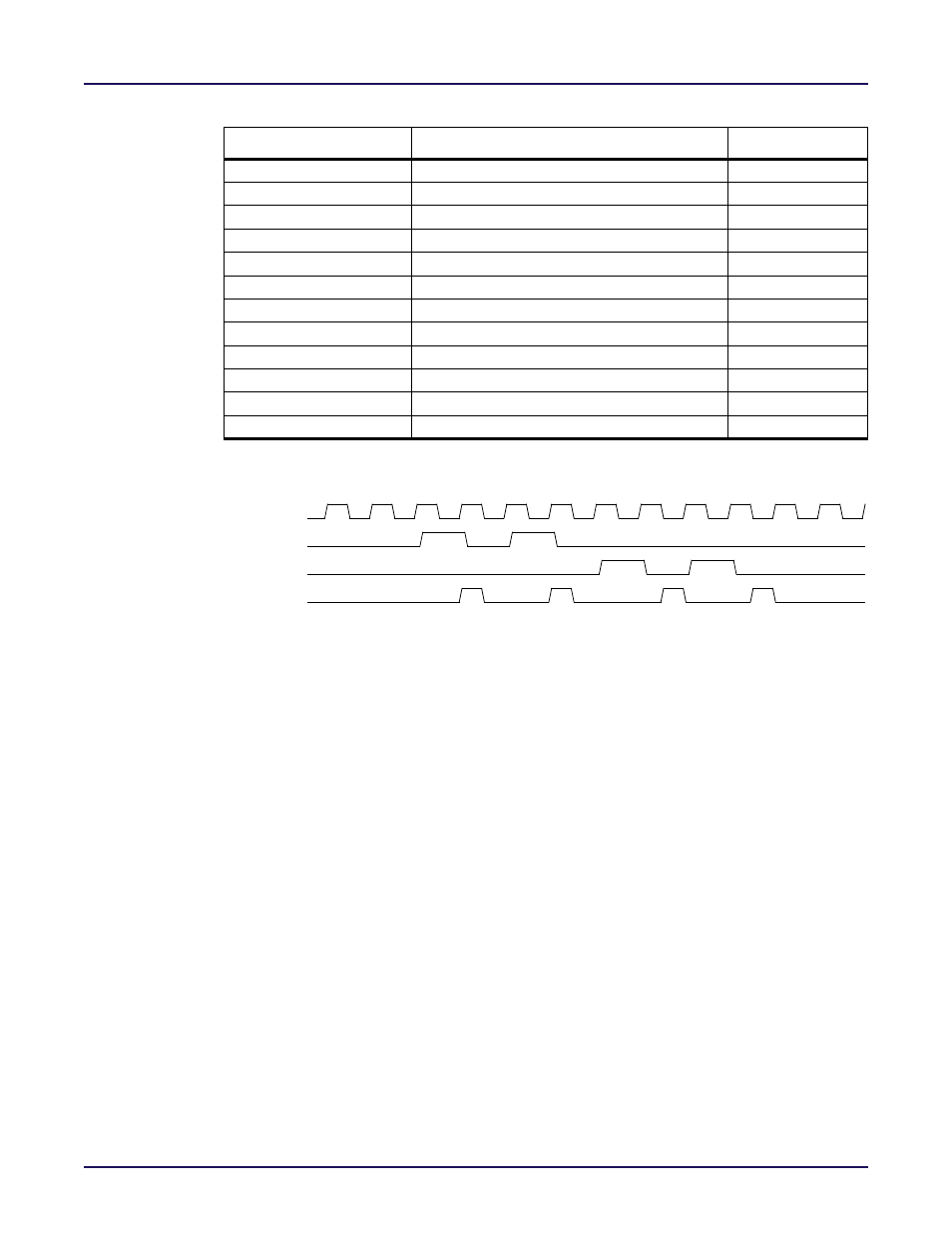

Table 1-38: Parameters

Parameter

Defined Values

Default Value

location

iostandard

“LVCMOS18”

drive

rstmode

rstvalue

slew

keepmode

hysteresis

open_drain

“true”, “false”

“false”

pvt_comp

“none”, “own”

“none”

odt

“off”, “on”

“off”

termination

“50”, “60”, “75”, “100”, “120”, “240”

“50”

Figure 1-17: OPAD_D2 Output Timing Diagram (assumes data_en = 1’b1)

Verilog Instantiation Template

OPAD_D2 #(.location(""),

.iostandard("LVCMOS18"),

.drive("16"),

.rstmode("async"),

.rstvalue("low"),

.slew("slow"),

.open_drain("false"),

.pvt_comp("none"))

instance_name (.pad(user_pad), .dina(user_dina), .dinb(user_dinb),

.data_en(user_data_en), .rstn(user_rstn), .clk(user_clk));

“

““

See

"2", "4", "6", "8", "12", "16"

"16"

“sync”, “async”

“async”

“low”, “high”

“low”

“fast”, “slow”

“slow”

"pullup", "pulldown", "none"

“none”

"none", "schmitt"

“none”

clk

dina

dinb

pad