Heading3 - rst_sync_mode, Heading3 - wrrst_sync_stages, Stage depth – Achronix Speedster22i User Macro Guide User Manual

Page 180: Rst_sync_mode, Wrrst_sync_stages

Memories

LRAMFIFO

Speedster22i Macro Cell Library

PAGE 163

transferring the Read Pointer across clock domains. As an example, setting rdptr_sync_stages

to 2’b00 configures the read pointer synchronization circuit to have two back‐to‐back registers

in the Read Pointer Synchonizer. The default value of the rdptr_sync_stages parameter is

2’b00.

Table 6-53: Mapping rdptr_sync_stages Parameter Settings to Synchronization Stage Depth

rdptr_sync_stages

Read Pointer Synchronization Stage Depth

2’b00

2

2’b01

3

2’b10

4

2’b11

5

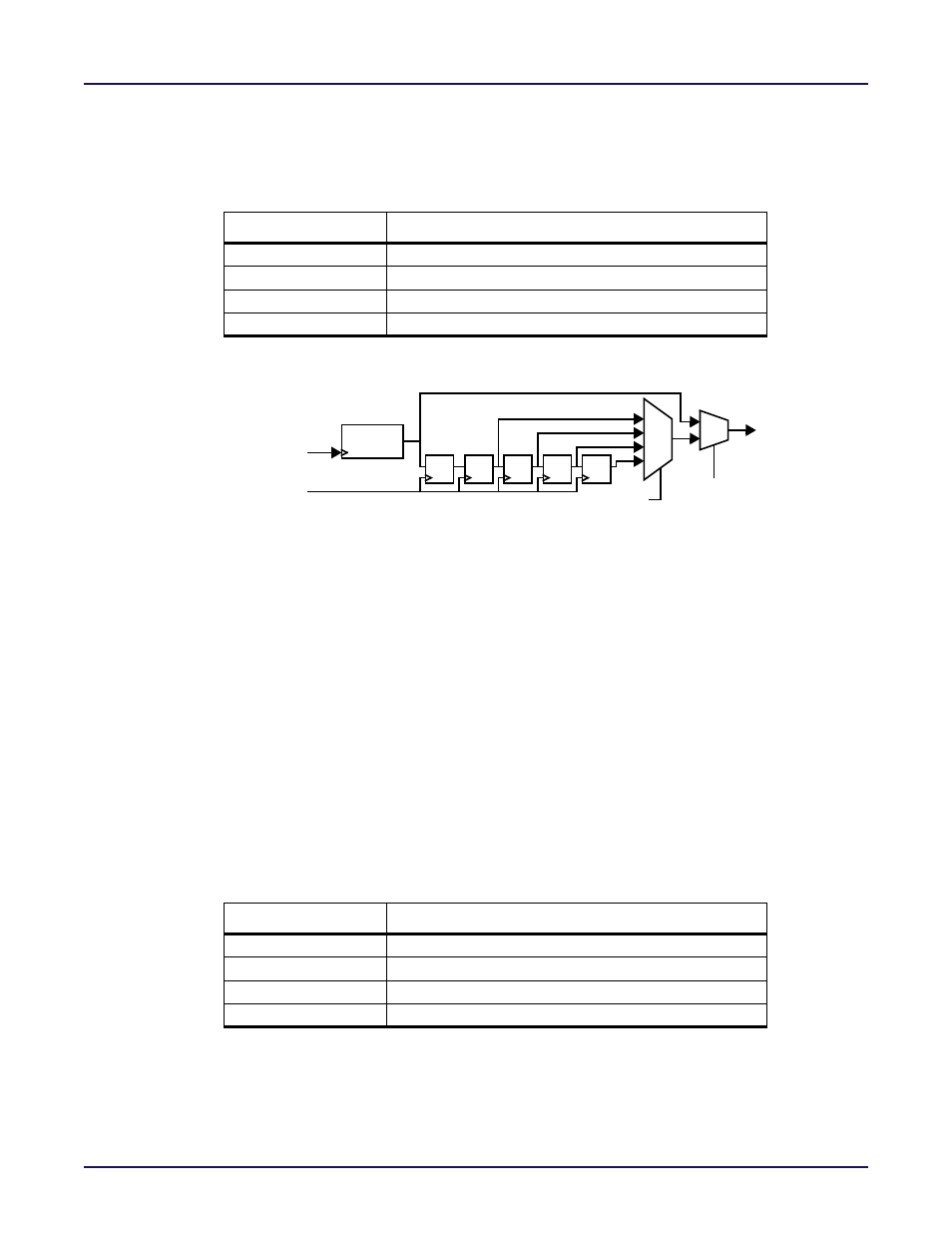

Figure 6-34: Read Pointer Synchronizer Block Diagram

rst_sync_mode

The rst_sync_mode parameter affects the behavior of the reset operation of the write and read

pointers. When the rst_sync_mode parameter is set to 1’b0, both the read and write pointers

resets utilize the Reset Synchronizer circuitry. When the rst_sync_mode parameter is set to

1’b1 the rstn input must be synchronous to the wrclk/rdclk clock driving the FIFO. The default

value of the rst_sync_mode parameter is 1’b0.

wrrst_sync_stages

The wrrst_sync_stages parameter defines the number of stages of registers used to

synchronize the rstn input pin to the rdclk clock domain. The value of the wrrst_sync_stages

parameter is only used if the rst_sync_mode is set to 1’b0. The mapping of the

wrrst_sync_stages parameter value to the number of sychronization stages is defined in

6‐54: Mapping wrrst_sync_stages Parameter Settings to Synchronization Stage Depth

where each stage corresponds to a register in

Figure 6‐35: Write Pointer Reset Input

. For example, setting wrrst_sync_stages to 2’b00 configures the rstn

synchronization circuit to have two back‐to‐back registers in the Write Reset Synchonizer. The

default value of the wrrst_sync_stages parameter is 2’b00.

Table 6-54: Mapping wrrst_sync_stages Parameter Settings to Synchronization Stage Depth

wrrst_sync_stages

Write Reset Synchronization Stage Depth

2’b00

2

2’b01

3

2’b10

4

2’b11

5

Read

Pointer

Read Pointer Synchronizer

d q

d q

d q

d q

d q

rdclk

wrclk

ptr_sync_mode

rdptr_sync_stages

Synchronized

Read Pointer

used for flag

00

01

10

11

0

1

calculations