Table - table 6-46: bram80keccfifo pin description – Achronix Speedster22i User Macro Guide User Manual

Page 171

Memories

BRAM80KECCFIFO

Speedster22i Macro Cell Library

PAGE 154

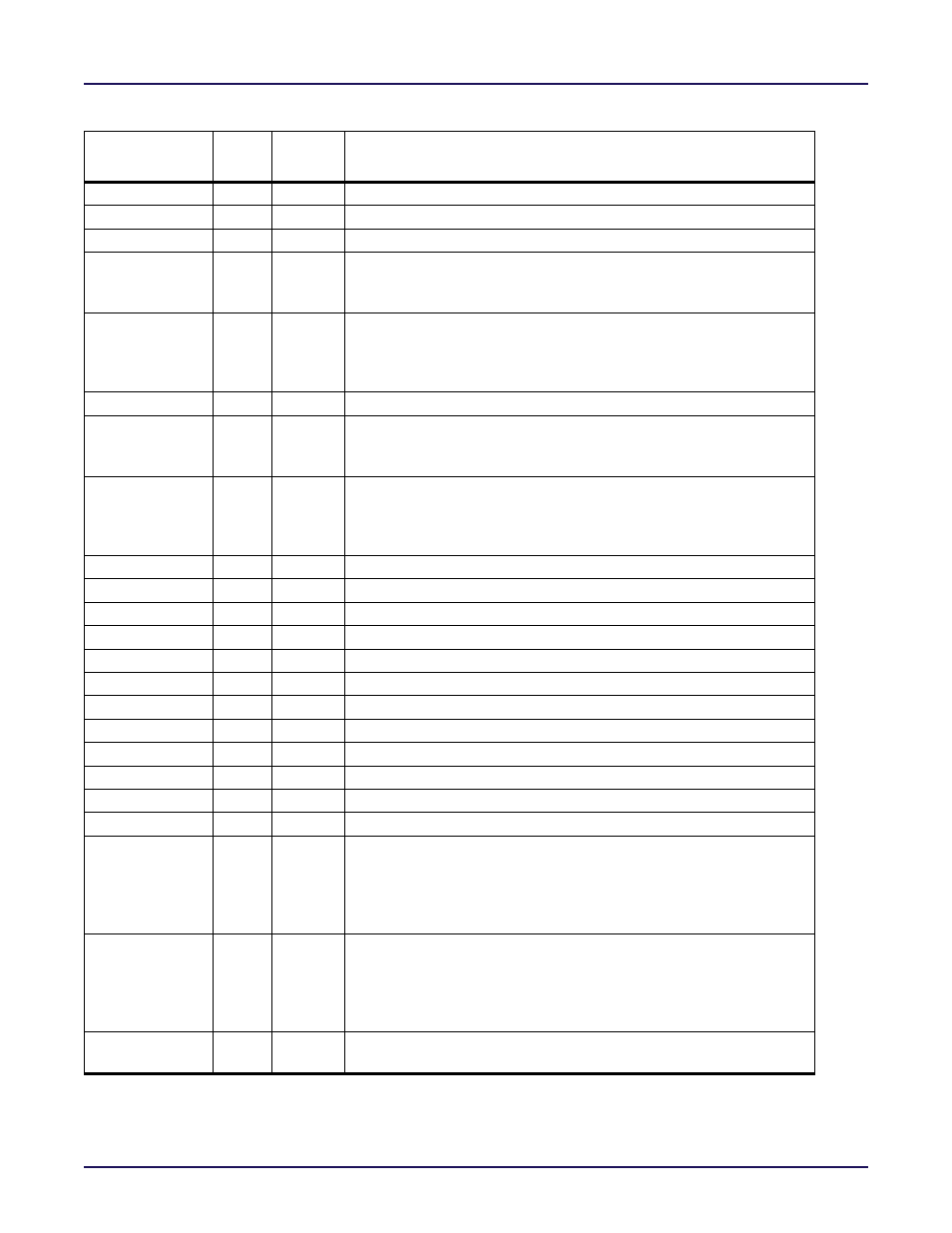

Table 6-46: BRAM80KECCFIFO Pin Description

Name

Type

Clock

Domain

Description

din[31:0]

Write port data input.

dinp[3:0]

Write port parity input (may be used for data).

dinpx[3:0]

Write port extended parity input (may be used for data).

wren

Write enable (active-high). Data is written into the FIFO at the next

active edge of the write clock when wren is driven high, as long as the

full flag is not asserted.

wrrst

Write port FIFO reset (programmable, default active-high). Asserting

the wrrst signal resets the FIFO to clear both read and write pointers

and set the FIFO to the empty condition. The contents of the FIFO are

not affected by the wrrst signal.

wrclk

Write clock. (programmable, default rising edge = 1’b1).

rden

Read enable (active-high). Data is read from the FIFO at the next

active edge of the clock when the rden is driven high, as long as the

empty flage is not asserted.

rdrst

Read port FIFO reset (programmable, default active-high). Asserting

the rdrst signal resets the FIFO to clear both read and write pointers

and set the FIFO to the empty condition. The contents of the FIFO are

not affected by the rdrst signal.

rdclk

Read clock (programmable, default rising edge = 1’b1).

outregce

Output register clock enable (active-high).

rstreg

Output register reset (programmable, default active-high).

dout[31:0]

Read port dout output.

doutp[3:0]

Read port parity output (used for data).

doutpx[3:0]

Read port extended parity output (used for data).

empty

Empty flag (active-high).

full

Full flag (active-high).

almost_empty

Almost Empty flag (active-high).

almost_full

Almost Full flag (active-high).

write_err

Write Error flag (active-high).

read_err

Read Error flag (active-high).

sbit_error

Single Bit Error. (active-high). The sbit_error signal is asserted during a

read operation when a single bit error is detected and the corrected

word is output on the dout pins. The memory contents are not

corrrected by the error correction circuitry. The sbit_error signal is

aligned with the associated read data word.

dbit_error

Double Bit Error. (active-high). The dbit_error signal is asserted during

a read operation when a two-bit error is detected. In the case of a two-

bit error condition, the uncorrected read data word is output on the

dout pins. The dbit_error signal is asserted one cycle after the associ-

ated read data word.

rdaddrecc[10:0]

Read Address. The rdaddrecc output is the 11-bit address of the read

data word.

input

wrclk

input

wrclk

input

wrclk

input

wrclk

input

prog.

input

wrclk

input

rdclk

input

prog.

input

rdclk

input

rdclk

input

rdclk

output

rdclk

output

rdclk

output

rdclk

output

rdclk

output

wrclk

output

rdclk

output

wrclk

output

wrclk

output

rdclk

output

rdclk

output

rdclk

output

rdclk