Achronix Speedster22i User Macro Guide User Manual

Page 162

Memories

BRAM80KFIFO

Speedster22i Macro Cell Library

PAGE 145

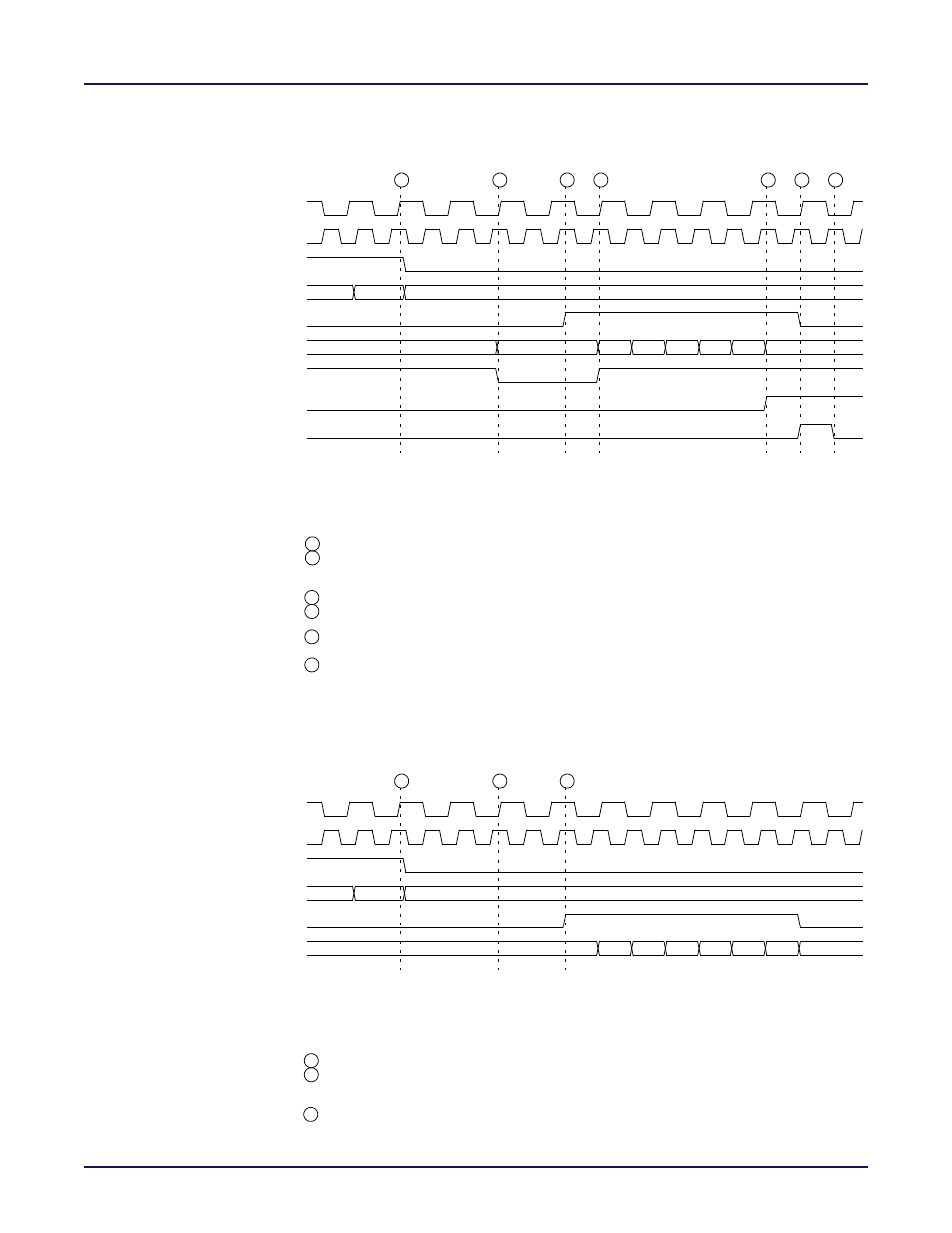

Reading from an Almost Empty FIFO (en_rd_when_empty = 1’b0, fwft = 1’b1)

Figure 6-19: Reading From an Almost Empty FIFO (en_rd_when_empty = 1’b0, fwft = 1’b1)

Reading from an Almost Empty FIFO (en_rd_when_empty = 1’b1)

Figure 6-20: Reading From an Almost Empty FIFO (en_rd_when_empty = 1’b1)

wrclk

rdclk

wren

rden

dout

almost_empty

read_err

1. Almost Empty Offset programmed for 6 40-bit words (aempty_offset = 17’h00004)

Note: This timing diagram assumes:

2. wptr_sync_stages = 2’b00

3. en_rd_when_empty = 1’b0

wrd 5

empty

A

B

C

D

A

Event : Finish writing 6 words to the FIFO.

Event : The almost_empty flag is deasserted one wrclk plus (wrptr_sync_stages + 3)

B

din

wrd 0

wrd 1

wrd 4

wrd 2 wrd 3 wrd 4 wrd 5

4. fwft = 1’b1

E

F

G

rdclk active clock edges after the sixth (wrd 5) word is presented at the din input

with wren high.

Event : Begin to read the six word from the FIFO.

C

Event : The almost_empty flag is asserted the cyle after the first read request, when

D

five words (including the one on the FIFO output) remain in the FIFO.

Event : The empty flag is asserted after the last (sixth) word is taken from the FIFO output.

E

The rden signal remains high, attempting to read an empty FIFO.

Event : The read_err signal is asserted the cycle after the attempt to read an empty FIFO.

F

The sixth (wrd 5) word remains at the dout output.

wrclk

rdclk

wren

rden

dout

Note: This timing diagram assumes:

1. wptr_sync_stages = 2’b00

2. en_rd_when_empty = 1’b1

wrd 5

A

B

C

A

Event : Finish writing 6 words to the FIFO.

Event : The almost_empty flag is deasserted one wrclk plus (wrptr_sync_stages + 3)

B

din

wrd 0 wrd 1

wrd 4

wrd 2 wrd 3 wrd 4 wrd 5

3. fwft = 1’b0

rdclk active clock edges after the sixth (wrd 5) word is presented at the din input

with wren high.

Event : Begin to read the six word from the FIFO.

C

wrd (note4)

4. The word read after the sixth word (wrd 5) will be the last word written to the address of:

(Address[wrd 5] + 1) modulo (maximum FIFO depth for programmed read_width)