Chaptertitle - chapter 1 – i/o cells, Chapter 1 – “i/o cells, Chapter 1 – i/o cells – Achronix Speedster22i User Macro Guide User Manual

Page 18

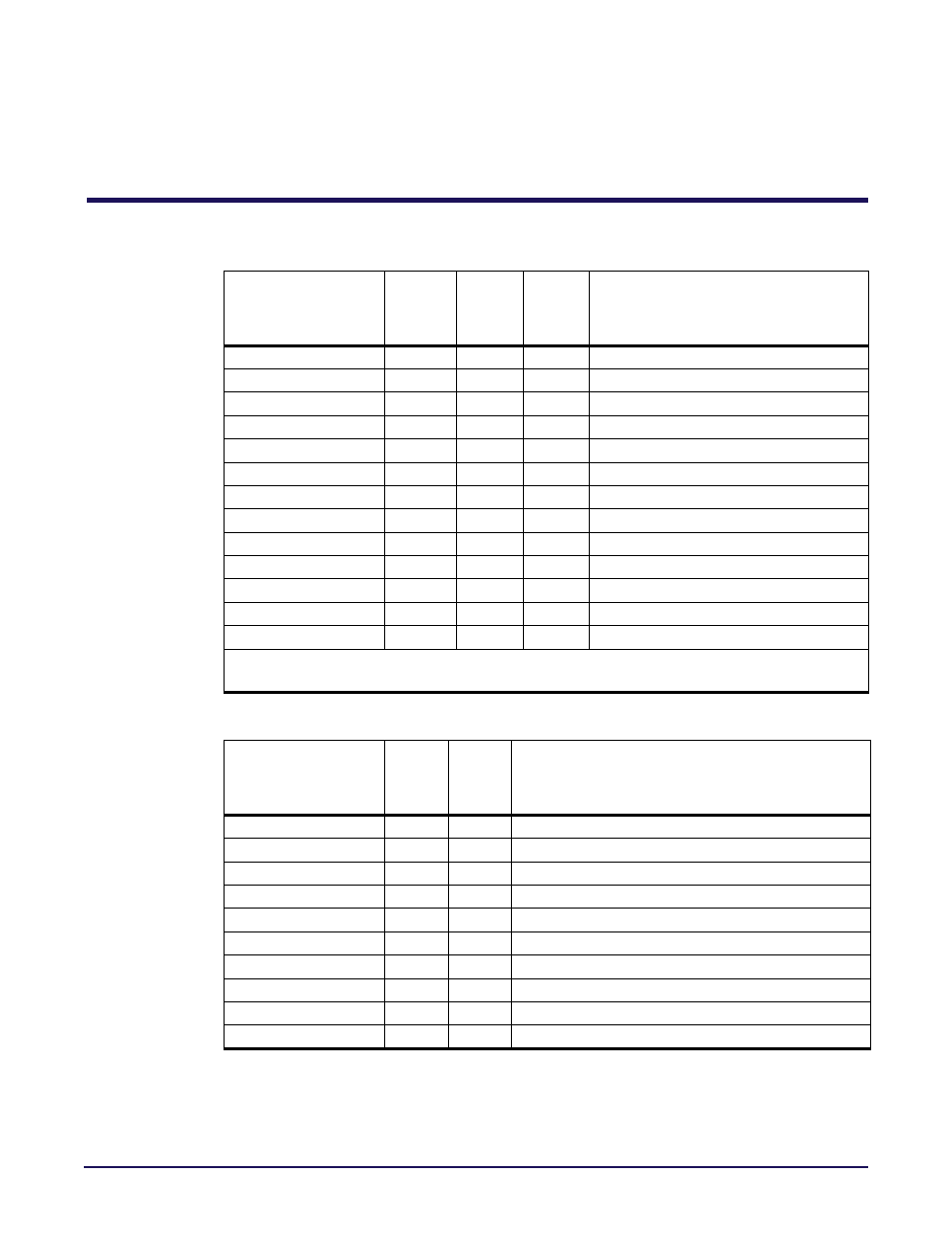

Table 1-1: Supported Single-Ended Voltage Standards

I/O Standard

Parameter

Output

V

DDO

(Volts)

Input

V

DDI

(Volts)

V

REF

(Volts)

(1)

Description

HSTL15_I

1.5

1.5

0.75

1.5V HSTL, type I

HSTL15_II

1.5

1.5

0.75

1.5V HSTL, type II

HSTL18_I

1.8

1.8

0.90

1.8V HSTL, type I

HSTL18_II

1.8

1.8

0.90

1.8V HSTL, type II

LVCMOS12

1.2

1.2

0.60

1.2V LVCMOS

LVCMOS15

1.5

1.5

0.75

1.5V LVCMOS

LVCMOS18

1.8

1.8

0.90

1.8V LVCMOS

SSTL15_I

1.5

1.5

0.75

1.5V SSTL, type I

SSTL15_II

1.5

1.5

0.75

1.5V SSTL, type II

SSTL18_I

1.8

1.8

0.90

1.8V SSTL, type I

SSTL18_II

1.8

1.8

0.90

1.8V SSTL, type II

POD18

1.8

1.8

0.90

1.8V POD

POD15

1.5

1.5

0.75

1.5V POD

Notes:

1. Set by V

REF

Pin.

Table 1-2: Supported Differential Voltage Standards

I/O Standard

Parameter

Output

V

DDO

(Volts)

Input

V

DDI

(Volts)

Description

DIFF_HSTL15_I

1.50

1.50

Differential 1.5V HSTL, type I

DIFF_HSTL15_II

1.50

1.50

Differential 1.5V HSTL, type II

DIFF_HSTL18_I

1.80

1.80

Differential 1.8V HSTL, type I

DIFF_HSTL18_II

1.80

1.80

Differential 1.8V HSTL, type II

DIFF_SSTL15_I

1.50

1.50

Differential 1.5V SSTL, type I

DIFF_SSTL15_II

1.50

1.50

Differential 1.5V SSTL, type II

DIFF_SSTL18_I

1.80

1.80

Differential 1.8V SSTL, type I

DIFF_SSTL18_II

1.80

1.80

Differential 1.8V SSTL, type II

HT1.0

1.20

1.20

Differential HyperTransport 1.0

LVDS

1.8

1.8

LVDS (Low Voltage Differential Signalling)

Speedster Macro Cell Library

PAGE 1

Chapter 1 – I/O Cells