Heading1 - bram80kecc, Figure - figure 6-22: logic symbol, Figure - figure 6-23: bram80kecc block diagram – Achronix Speedster22i User Macro Guide User Manual

Page 164: Bram80kecc

Memories

BRAM80KECC

Speedster22i Macro Cell Library

PAGE 147

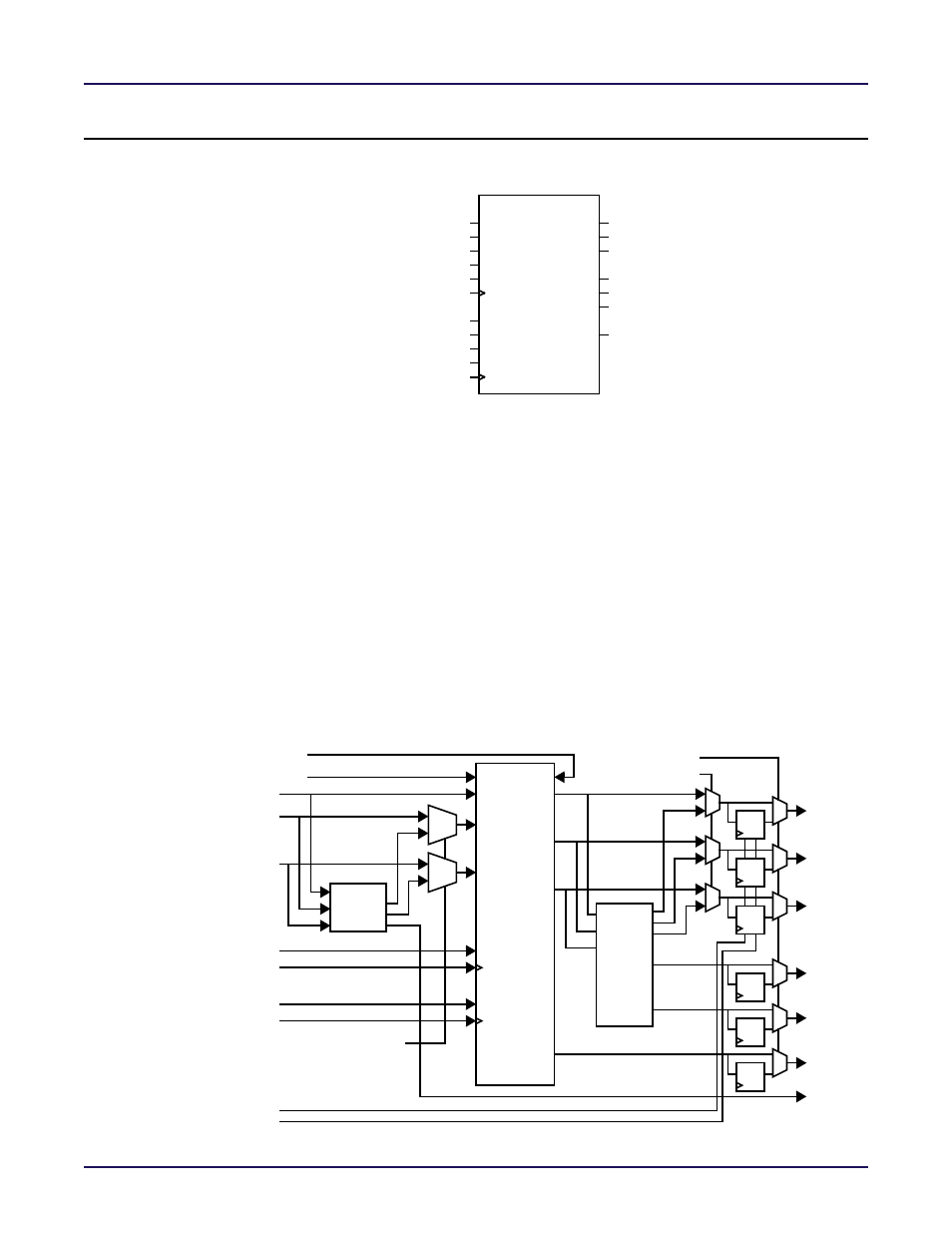

BRAM80KECC

80k-bit Simple Dual-Port Memory with Error Correction

BRAM80KECC

rdaddr[10:0]

dout[31:0]

rdclk

sbit_error

wraddr[10:0]

din[31:0]

wren

wrclk

enc_parity[6:0]

dinp[3:0]

dinpx[3:0]

doutp[3:0]

doutpx[3:0]

rden

rstreg

outregce

dbit_error

rdaddrecc[10:0]

Figure 6-22: Logic Symbol

The BRAM80KECC implements an 2kx32 simple dual‐ported memory block with error

correction codes (ECC). The embedded error correction encoder generates seven parity bits

and stores it alongside each word written into the memory. During the read operations, the

error correction decoder reads the seven parity bits and the 32 data bits to provide error

correction for all single‐bit errors and error detection without correction for all two‐bit errors.

Both the error correction encoder and the error correction decoder may be enabled separtely

to allow the ECC circuitry to be used outside of the BRAM memory block.

Although the embedded ECC circuitry corrects single‐bit errors upon reading the data, the

contents of the memory block do not get corrected. In order to provide the user a means to

correct the memory contents, the read memory address is also available alongside the read

data on the rdaddrecc outputs.

To increase the speed of the ECC memory accesses, an optional output register, complete with

reset and clock enable inputs, is available to the user. The use of the output register will incur

a single additional cycle of read latency.

Figure 6-23: BRAM80KECC Block Diagram

32-bit

ECC

Encoder

2kx40

Dual-Port

Memory

din[31:0]

wren

wrclk

rdclk

outregce

rstreg

dinp[3:0]

dinpx[3:0]

rden

rdaddr[10:0]

wraddr[10:0]

d q

32-bit

ECC

Decoder

d q

d q

d q

din

dinp

dinpx

dout

doutp

doutpx

sbit_error

dbit_error

rdaddrecc

d q

dbit_error

sbit_error

dout

doutp

doutpx

waddr raddr

d q

enc_parity

[10:0]

[6:0]

encoder_enable

decoder_enable

en_out_reg

[31:0]

[3:0]

[3:0]