Rockwell Automation 20D PowerFlex 700S AC Drives with Phase II Control Programming Manual User Manual

Page 95

Rockwell Automation Publication 20D-PM001C-EN-P - July 2013

95

Programming and Parameters

Chapter 2

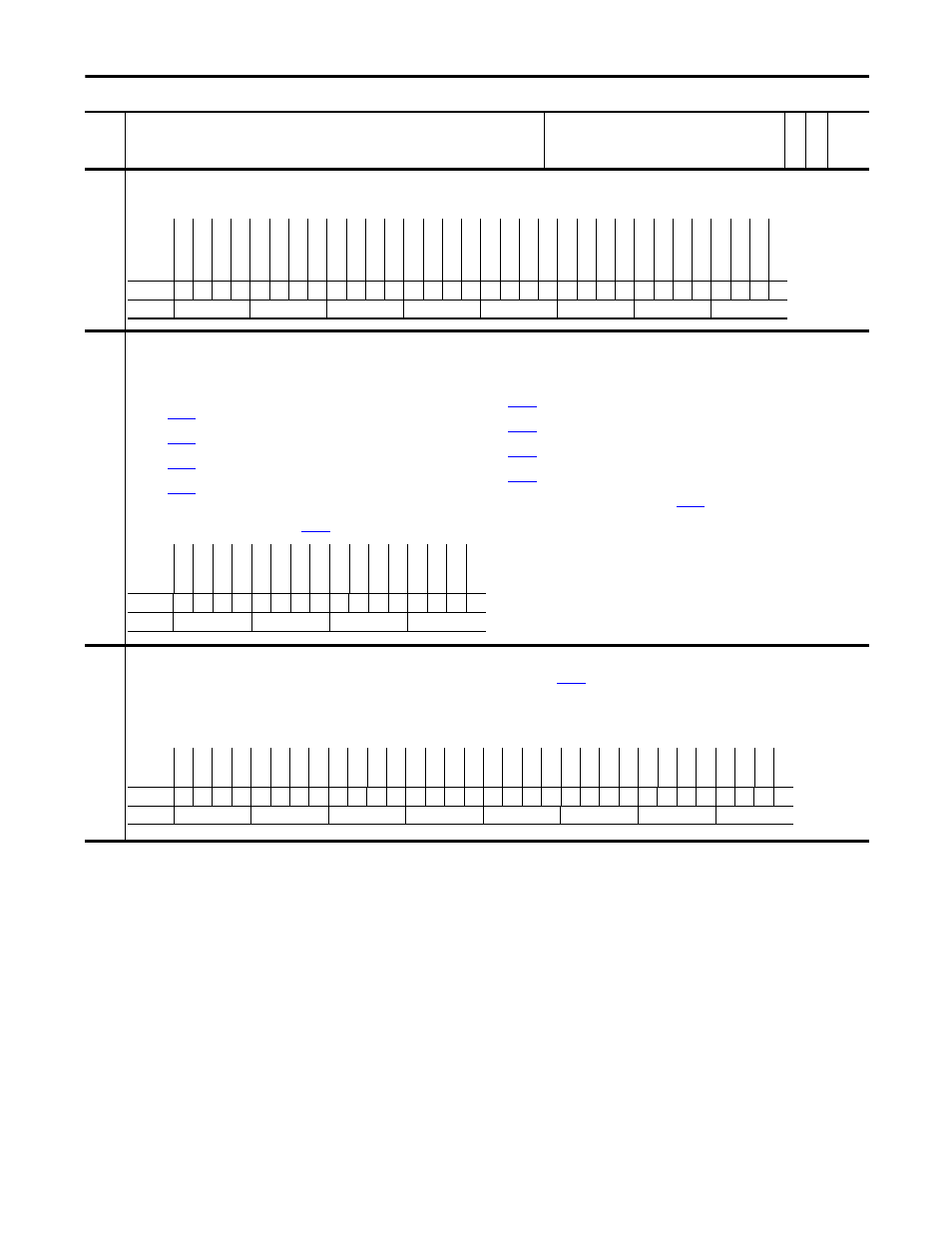

555 MC

Status

Indicates the status of the Motor Control (MC) Processor and related functions.

Note: Changed bit 18 from “Reserved” to “Vqs Reg Act” for firmware version 3.003.

556

Trend Control

Set bits to configure the Data Trend function:

• Bit 0 “Enbl Collect” - Trend data collection begins on the rising edge of this bit and continues until either this bit is set low or the trend data has been completely collected. This bit should be

cleared following either the 'Triggered' status or 'Complete' status in order to complete the trend sequence. This bit can also be cleared at any time to force the trend data sampling to stop and

set the 'Complete' status bit.

• Setting bit 1 “In1 Real” - specifies the Real data type for Trend Input 1. The source for Real data is

[Trend In1 Real]. Clearing the bit specifies the Integer data type. The source for Integer

data is

[Trend In1 DInt].

• Setting bit 2 “In2 Real” - specifies the Real data type for Trend Input 2. The source for Real data is

[Trend In2 Real]. Clearing the bit specifies the Integer data type. The source for Integer

data is

[Trend In2 DInt].

• Setting bit 3 “In3 Real” - specifies the Real data type for Trend Input 3. The source for Real data is

[Trend In3 Real]. Clearing the bit specifies the Integer data type. The source for Integer

data is

[Trend In3 DInt].

• Setting bit 4 “In4 Real” - specifies the Real data type for Trend Input 4. The source for Real data is

[Trend In4 Real]. Clearing the bit specifies the Integer data type. The source for Integer

data is

[Trend In4 DInt].

• Setting bit 15 “Auto Output” causes the trend output parameters to automatically cycle through the entire trend buffer at the rate specified in

[Trend Rate]. Typically, you link the output

to an analog output for display on an oscilloscope.

• Auto output is accomplished by writing to

[TrendBuffPointer]. Clearing this bit requires manual selection of Par 569 [TrendBuffPointer] to view the trend buffer contents.

557

Trend Status

Bits indicate the status of the Data Trend function:

• Bit 1 “Triggered” indicates a Trend Trigger event has been detected. This bit will clear in response to the rise of

[Trend Control], bit 0 “Enbl Collect”.

• Bit 2 “Complete” indicates all the post trigger data samples have been gathered and the trend buffers are full. It will also be set if the Par 556 [Trend Control], bit 0 “Enbl Collect” is cleared before

the trigger occurs. The trend data outputs will be updated from the contents of the trend buffer data when this bit is set. Par 556 [Trend Control], bit 0 “Enbl Collect” can be cleared after this bit

is set without affecting the trend data buffer contents. This bit will clear in response to the rise of Par 556 [Trend Control], bit 0 “Enbl Collect”. The trend outputs will be forced to zero while this bit

is clear.

No.

Name

Description

Values

Link

able

Re

ad

-Write

Da

ta

T

yp

e

Options

Mi

n V

qs

MaxDCBus

V

qs

MaxMot

or V

qs

Max V

ds

Mi

n V

ds

Sr

Ls

sW

sL

im

it

Slip

L

imit

Re

gen

Iq

s L

im

it

Fl

dW

eak

ening

MC FW Gr

oup2

Re

se

rv

ed

Re

se

rv

ed

Vq

s R

eg

A

ct

Flu

xR

at

io

Ref

Co

m

m

an

d L

im

DC

Bu

s L

ow

MC T

est Mode

Pr

eChr

g Re

q

PW

M E

n

Pr

eChr

g D

one

Flu

x En

To

rq

ue

E

n

Cha

nge Di

r

MC C

omm

is

Fl

t

MC C

omm

is

Run

MC F

ault

MC R

ea

dy

Ba

se

Bl

oc

kR

eq

To

rq

ue

Ru

nR

eq

Flu

x Ru

n R

eq

MC E

n Req

Default

0

0

0

0

0

0

0

0

0

0

0

x

x

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

0 = False

1 = True

Options

Au

to

O

ut

pu

t

Re

ser

ve

d

Re

ser

ve

d

Re

ser

ve

d

Re

ser

ve

d

Re

ser

ve

d

Re

ser

ve

d

Re

ser

ve

d

Re

ser

ve

d

Re

ser

ve

d

Re

ser

ve

d

In 4 R

ea

l

In 3 R

ea

l

In 2 R

ea

l

In 1 R

ea

l

En

bl

C

ol

le

ct

Default

0

x

x

x

x

x

x

x

x

x

x

0

0

0

0

0

Bit

15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

0 = False

1 = True

Options

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Co

m

pl

et

e

Trigger

ed

Re

se

rv

ed

Default

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

0

0

x

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

0 = False

1 = True