Rockwell Automation 20D PowerFlex 700S AC Drives with Phase II Control Programming Manual User Manual

Page 56

56

Rockwell Automation Publication 20D-PM001C-EN-P - July 2013

Chapter 2

Programming and Parameters

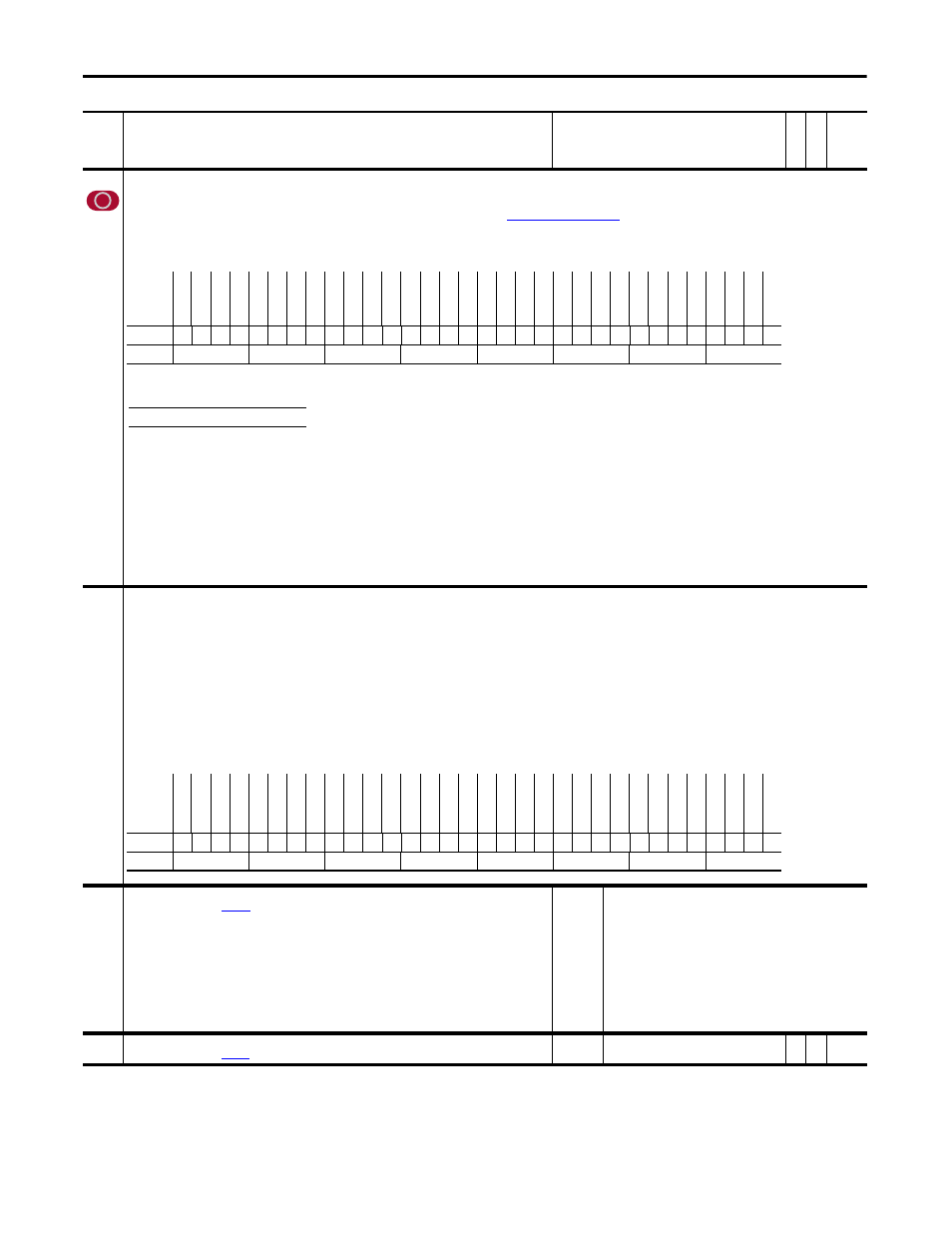

259 Stegmann0

Cnfg

Configures the Stegmann Hi-Resolution Encoder Feedback Option.

• Bit 5 “Direction” determines counting direction. If clear, direction is forward or up. If set, the direction is reverse or down.

• Bits 10 “SmplRate bt0” -12 “SmplRate bt2” configure the Finite Impulse Response (FIR) Filter (see

Table 259A: FIR Filter Settings

). This setting reduces the effect of noisy feedback on the system.

Refer to the Speed/Position Feedback section of the PowerFlex® 700S with Phase II Control Reference Manual, publication PFLEX-RM003 for details.

Notes: Bit 11 “SmplRate bt1” is set to 0 = False by default for firmware version 1.11 and is set to 1 = True by default for firmware version 2.003. This parameter was changed to non-linkable for

firmware version 3.001.

260 Stegmann0

Status

Indicates faults on the Stegmann Hi-Resolution Encoder Feedback Option.

• Bit 8 “Open Wire” indicates an open wire fault.

The feedback option card checks for a pre-determined constant value. If this value is not within tolerances, an open wire fault is declared. A quadrature check also is done. If an error occurs during

the check, the ope wire check is aborted. If 3 quadrature errors occur in succession, the open wire check will complete and the constant value checked again. If this value is not within tolerances,

the fault is declared.

• Bit 9 “PowerSup Er” indicates the failure of the power supply.

• Bit 10 “PwrUpDiag Er” indicates the option board failed its power-up diagnostic test.

The pattern on the FPGA must be identical to the pattern written from the DSP, or the board status test will fail.

• Bit 11 “MsgChksum Er” indicates a message checksum fault.

The check sum associated with the Heidenhain encoder must be correct and acknowledged by the feedback option card.

• Bit 12 “Time Out Err” indicates a RS-485 time-out fault.

This check requires information to be sent from the encoder to the feedback option card within a specified time. Typical times are about 10 clock cycles before an error is detected. This check is

done only at power-up.

261 Steg&Hiedn

TPSel

Selects data displayed by

[Steg&Hiedn TPDta].

• Hh0 Edge Time - Latency counter value, not used for Hi-Resolution Feedback Option.

• Hh0 dEdge - Change in edge counts for one 500 microsecond update. At constant speed, this value should be

constant.

• Hh0 dTime - Change in update time. This value should be constant, 500 microseconds.

• Hh0 EPR - This value should be 1,048,576 counts per revolution-this is a constant value.

• Hh0 nMax - This is a scaled value of 2.

• Hho Delta2Err - Derivative of value 2.

Default:

Options:

0 =

0 =

1 =

2 =

3 =

4 =

5 =

6 =

7 =

8 =

9 =

“Zero”

“Zero”

10 = “Reserved”

“St0 EdgeTime”

11 = “Hh0 EdgeTime”

“St0 dEdge”

12 = “Hh0 dEdge”

“St0 dTime”

13 = “Hh0 dTime”

“St0 EPR”

14 = “Hh0 EPR”

“St0 EdgeMode”

15 = “Hh0 EdgeMode”

“St0 nMax”

16 = “Hh0 nMax”

“St0 Delta2Er”

17 = “Hh0 Delta2Er”

“Reserved”

“Reserved”

262 Steg&Hiedn

TPDta

Displays data selected by

[Stegmann0 Status].

Default:

Min/Max:

0

-/+32768

RO 16-bit

Integer

No.

Name

Description

Values

Link

able

Re

ad

-Write

Da

ta

T

yp

e

Options

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Sm

plRa

te

bt2

Sm

plRa

te

bt1

Sm

plRa

te

bt0

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

SW Reset

Dir

ec

tio

n

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Default

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

0

0

0

x

x

x

0

0

x

x

x

x

x

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

0 = False

1 = True

Table 259A: FIR Filter Settings

Bit 12 11 10 Taps

0

0

0 1

0

0

1 2

0

1

0 4

0

1

1 8

1

0

0 16

1

0

1 32

1

1

0 64

1

1

1 127

Options

Res

er

ve

d

Res

er

ve

d

Res

er

ve

d

Res

er

ve

d

Res

er

ve

d

Res

er

ve

d

Res

er

ve

d

Res

er

ve

d

Res

er

ve

d

Res

er

ve

d

Res

er

ve

d

Res

er

ve

d

Res

er

ve

d

Res

er

ve

d

Res

er

ve

d

Res

er

ve

d

Res

er

ve

d

Res

er

ve

d

Res

er

ve

d

Ti

m

e O

ut

E

rr

Ms

gCh

ksu

m

Er

Pw

rU

pDia

g E

r

Po

w

er

Su

p E

r

Op

en

W

ire

Res

er

ve

d

Res

er

ve

d

Res

er

ve

d

Res

er

ve

d

Res

er

ve

d

Res

er

ve

d

Res

er

ve

d

Res

er

ve

d

Default

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

0

0

0

0

0

x

x

x

x

x

x

x

x

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

0 = False

1 = True