Rockwell Automation 20D PowerFlex 700S AC Drives with Phase II Control Programming Manual User Manual

Page 66

66

Rockwell Automation Publication 20D-PM001C-EN-P - July 2013

Chapter 2

Programming and Parameters

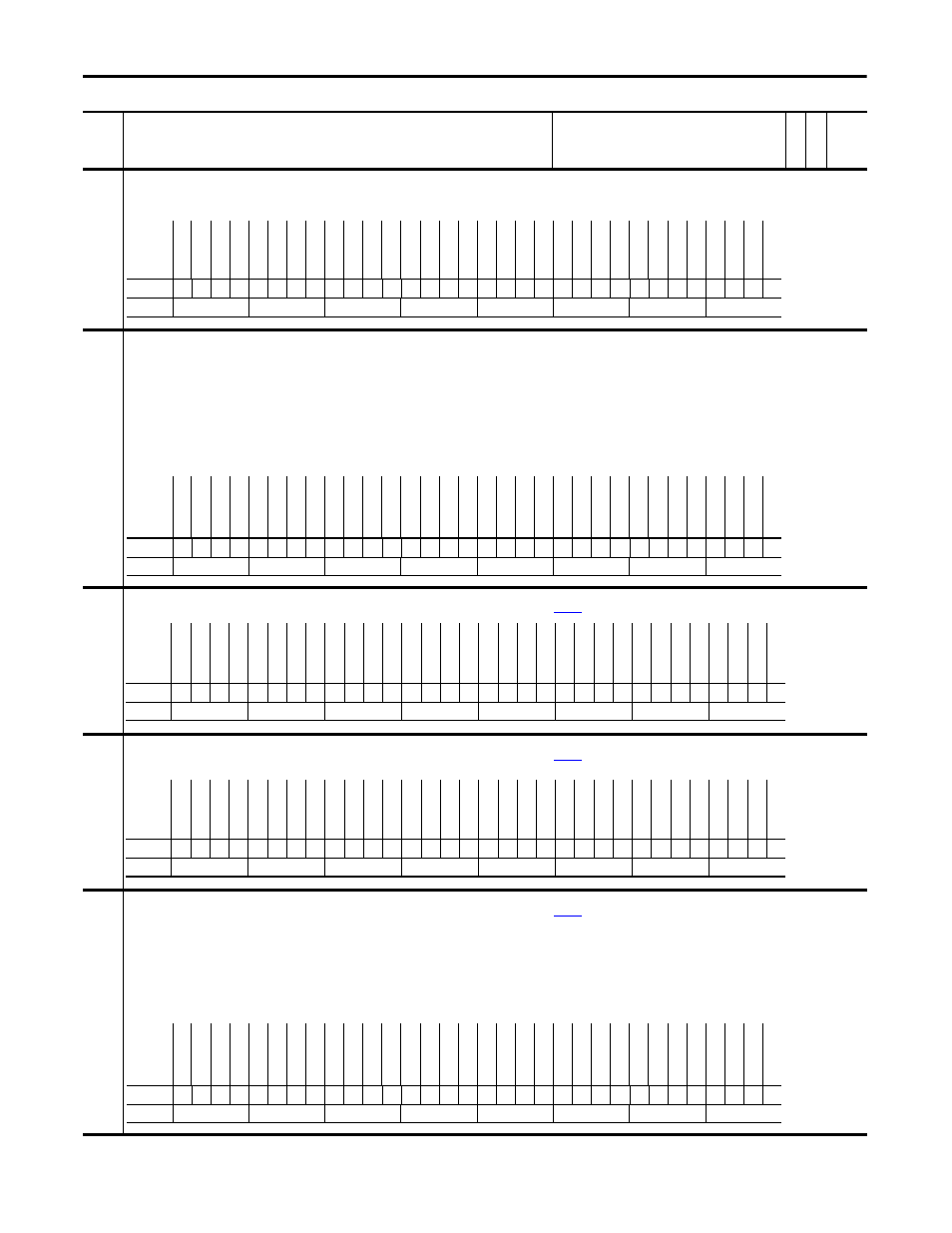

321 Exception

Event2

Indicates the presence of certain drive anomalies. Configure the drive's response to these events by entering values in the parameters of the fault/alarm configuration group of the utility file.

Note: Changed bit 14 to “NonCnfgAlarm” for firmware version 3.003.

322 Exception

Event3

Indicates the presence of certain drive anomalies. Configure the drive's response to these events by entering values in the parameters of the fault/alarm configuration group of the utility file.

• Bit 11 “HH HW Ver” is sed to indicate a High Horsepower hardware version fault.

• Bit 12 “HH CurUnblnc” is used to indicate a High Horsepower output current unbalanced fault.

• Bit 13 “HH VltUnblnc” is used to indicate a High Horsepower Bus voltage unbalanced fault.

• Bit 29 “AnlgIn1 Loss” is used to indicate an Analog Input 1 loss fault.

• Bit 30 “AnlgIn2 Loss” is used to indicate an Analog Input 2 loss fault.

• Bit 31 “AnlgIn3 Loss” is used to indicate an Analog Input 3 loss fault.

Notes: Bits 16, 20 and 23 were added for firmware version 2.004. Bits 11, 12, 13, 29, 30 and 31 were added for firmware version 3.001. Changed bits 11, 12, 13, 21, and 28 to “NonCnfgAlarm” for

firmware version 3.003. Bit 14 “NonCnfgAlarm” was added for firmware version 3.004.

323

Fault Status 1

Indicates the occurrence of exception events that have been configured as fault conditions. These events are from

[Exception Event1].

324

Fault Status 2

Indicates the occurrence of exception events that have been configured as fault conditions. These events are from

[Exception Event2]

Note: Changed bit 14 to “NonCnfgAlarm” for firmware version 3.003.

325

Fault Status 3

Indicates the occurrence of exception events that have been configured as fault conditions. These events are from

[Exception Event3].

• Bit 11 “HH HW Ver” is sed to indicate a High Horsepower hardware version fault.

• Bit 12 “HH CurUnblnc” is used to indicate a High Horsepower output current unbalanced fault.

• Bit 13 “HH VltUnblnc” is used to indicate a High Horsepower Bus voltage unbalanced fault.

• Bit 29 “AnlgIn1 Loss” is used to indicate an Analog Input 1 loss fault.

• Bit 30 “AnlgIn2 Loss” is used to indicate an Analog Input 2 loss fault.

• Bit 31 “AnlgIn3 Loss” is used to indicate an Analog Input 3 loss fault.

Notes: Bits 16, 20 and 23 were added for firmware version 2.004. Bits 11, 12, 13, 29, 30 and 31 were added for firmware version 3.001. Changed bit 21 to “Drive Homing” and bit 28 to “+/- 12v Pwr”

for firmware version 3.003. Bit 14 “NonCnfgAlarm” was added for firmware version 3.004.

No.

Name

Description

Values

Link

able

Re

ad

-Write

Da

ta

T

yp

e

Options

Lg

x LinkC

hng

Lg

x C

lo

sed

Lg

x T

imeout

Lg

x O

utOfR

un

NetL

oss DPI6

NetL

oss DPI5

NetL

oss DPI4

NetL

oss DPI3

NetL

oss DPI2

NetL

oss DPI1

DP

I L

oss

P6

DP

I L

oss

P5

DP

I L

oss

P4

DP

I L

oss

P3

DP

I L

oss

P2

DP

I L

oss

P1

No C

tr

l Dev

c

NonC

nfgA

larm

In

te

rp S

ync

h

Enabl

eHe

al

th

NonC

nfgA

larm

Vo

ltF

dbk

Lo

ss

Bus

U

nde

rV

olt

Ri

de

th

ru

Ti

m

e

Slink Mult

Po

w

er

EE

C

ks

m

Br

ak

eO

L T

rip

PSC S

ys F

lt2

PSC S

ys F

lt1

Ctrl

EE C

ksm

MC C

omm

and

+/

- 1

2v

Pw

r

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

0 = False

1 = True

Options

An

lg

In

3 L

os

s

An

lg

In

2 L

os

s

An

lg

In

1 L

os

s

N

onC

nfgAlarm

Res

er

ve

d

Res

er

ve

d

Res

er

ve

d

Res

er

ve

d

N

onC

nfgAlarm

Res

er

ve

d

N

onC

nfgAlarm

Po

si

t E

rr

-Hr

d O

vr

Tr

vl

+H

rd O

vr

Tr

vl

-S

ft Ovr

Tr

vl

+Sf

t O

vr

Tr

vl

Res

er

ve

d

N

onC

nfgAlarm

N

onC

nfgAlarm

N

onC

nfgAlarm

N

onC

nfgAlarm

HH

P

w

rB

dT

em

p

HH

P

w

rE

E Er

HH

PrC

hr

gCntc

HH

P

w

rB

d Prc

HH

D

rv O

vr

ld

HH F

anF

dbkLs

HH

B

usWtch

D

g

HH

B

usC

RC

Er

HH

B

usL

in

kL

s

HH

B

usC

omD

ly

HH

In

Ph

as

eL

s

Default

0

0

0

0

x

x

x

x

0

x

0

0

0

0

0

0

x

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

0 = False

1 = True

Options

PW

M As

yn

ch

ro

Pr

ec

har

ge

E

r

MC F

irm

wa

re

PW

M Sh

or

t

VP

L/MC C

omm

O

verC

urr

ent

Gr

ound F

ault

Tr

an

s De

sa

t

Bus Ov

er

Vo

lt

MC C

omm

is

sn

O

ver F

req

Ine

rtia T

es

t

DS

P E

rr

or

DS

P Me

m E

rr

Ex

t F

ault In

In

v O

L T

rip

In

v O

L P

end

In

v O

Tmp

Tr

ip

In

v O

TmpP

end

Mot

or Sta

ll

Mtr OL

P

end

Mtr OL

T

rip

Po

w

er

L

os

s

SLink C

omm

SLink HW

Ctr

l EE Mem

FB Opt1 L

oss

FB Opt0 L

oss

Enc

dr1 L

oss

Enc

dr0 L

oss

SpdRef

D

ecel

Abs Ov

erS

pd

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

0 = False

1 = True

Options

Lg

x LinkChng

Lg

x C

lo

se

d

Lg

x T

imeout

Lg

x O

ut

O

fR

un

Net

Lo

ss DP

I6

Net

Lo

ss DP

I5

Net

Lo

ss DP

I4

Net

Lo

ss DP

I3

Net

Lo

ss DP

I2

Net

Lo

ss DP

I1

DPI

L

os

s P6

DPI

L

os

s P5

DPI

L

os

s P4

DPI

L

os

s P3

DPI

L

os

s P2

DPI

L

os

s P1

No

C

tr

l D

evc

N

onC

nfgAlarm

Inte

rp S

ynch

En

abl

eH

eal

th

N

onC

nfgAlarm

Vo

ltF

dbkL

oss

Bus

U

nderV

olt

Ride

thru

Ti

me

Slink Mult

Pow

erEE Cksm

Brak

eO

L T

rip

PSC S

ys

Fl

t2

PSC S

ys

Fl

t1

Ct

rl EE Ck

sm

M

C C

omma

nd

+/-

12v P

w

r

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

0 = False

1 = True

Options

An

lg

In

3 L

os

s

An

lg

In

2 L

os

s

An

lg

In

1 L

os

s

N

onC

nfgAlarm

Res

er

ve

d

Res

er

ve

d

Res

er

ve

d

Res

er

ve

d

N

onC

nfgAlarm

Res

er

ve

d

N

onC

nfgAlarm

Po

si

t E

rr

-Hr

d O

vr

Tr

vl

+H

rd O

vr

Tr

vl

-S

ft Ovr

Tr

vl

+Sf

t O

vr

Tr

vl

Res

er

ve

d

N

onC

nfgAlarm

N

onC

nfgAlarm

N

onC

nfgAlarm

N

onC

nfgAlarm

HH

P

w

rB

dT

em

p

HH

P

w

rE

E Er

HH

PrC

hr

gCntc

HH

P

w

rB

d Prc

HH

D

rv O

vr

ld

HH F

anF

dbkLs

HH

B

usWtch

D

g

HH

B

usC

RC

Er

HH

B

usL

in

kL

s

HH

B

usC

omD

ly

HH

In

Ph

as

eL

s

Default

0

0

0

0

x

x

x

x

0

x

0

0

0

0

0

0

x

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

0 = False

1 = True