Real divide (rdiv), Inputs, Figure 10.32— real divide function block – Watlow LogicPro User Manual

Page 168

Chapter 10: Function Blocks

LogicPro User’s Guide

152

Watlow Anafaze

Doc.# 28002-00 Rev 3.00

RC is the product value. RC contains the product of RA and RB

as long as the enable bit is True. The range of values this

Variable can assume is from -3.4x10

38

to 3.4x10

38

. If this

Variable is assigned a value out of these ranges, ENO is

disabled. RC reverts to its last valid value whenever ENO is

disabled.

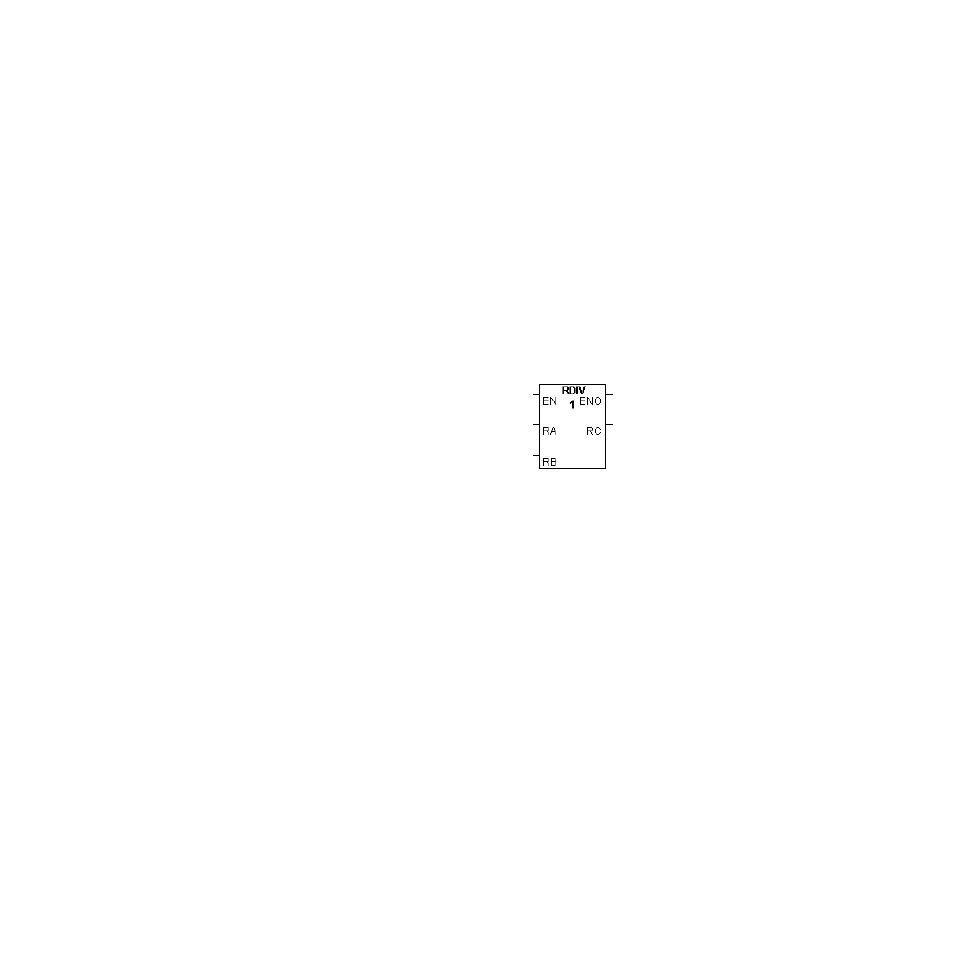

Real Divide (RDIV)

The Real Divide (RDIV) function block, shown in Figure

10.32, produces the quotient of two real Variable values.

RDIV calculates the quotient between one value (RA) which is

the dividend and another value (RB) which is the divisor and

places the result in another Variable (RC) when the enable bit

(EN) is True. The values of RA and RB can be preset to a

constant or assigned a Variable name, which allows their

value to change dynamically within the program.

Figure 10.32 Real Divide Function Block

Inputs

EN is the Real Divide enable bit. A True condition of this bit

causes the value of RA to be divided by the value of RB and the

result stored in RC. In a program using Ladder logic, the value

of EN is determined by the Boolean evaluation of elements

placed between the left power rail and EN in the function

block. In FBD programs, the value of EN is determined by the

Variable connected to EN. If no contacts are placed on the

rung before EN in a Ladder Diagram program, the value of EN

is always True. In FBD, all inputs must be connected to a

Variable.

RA is the dividend. The range of values this Variable can

assume is from -3.4x10

38

to 3.4x10

38

. If this Variable is

assigned a value out of these ranges, unpredictable results will

occur.

RB is the divisor. The range of values this Variable can assume

is from -3.4x10

38

to 3.4x10

38

. If this Variable is assigned a

value out of these ranges, unpredictable results will occur.

Also, if RB is assigned a value of zero (0), the enable out bit

becomes False and RC retains its previous value.