GW Instek PSB-2000 Series User Manual User Manual

Page 136

PSB-2000 Series User Manual

136

(SRE) is set 1 at this time, bit 6 (MSS) of the status

byte register is set to 1 and a service request (SRQ)

is generated.

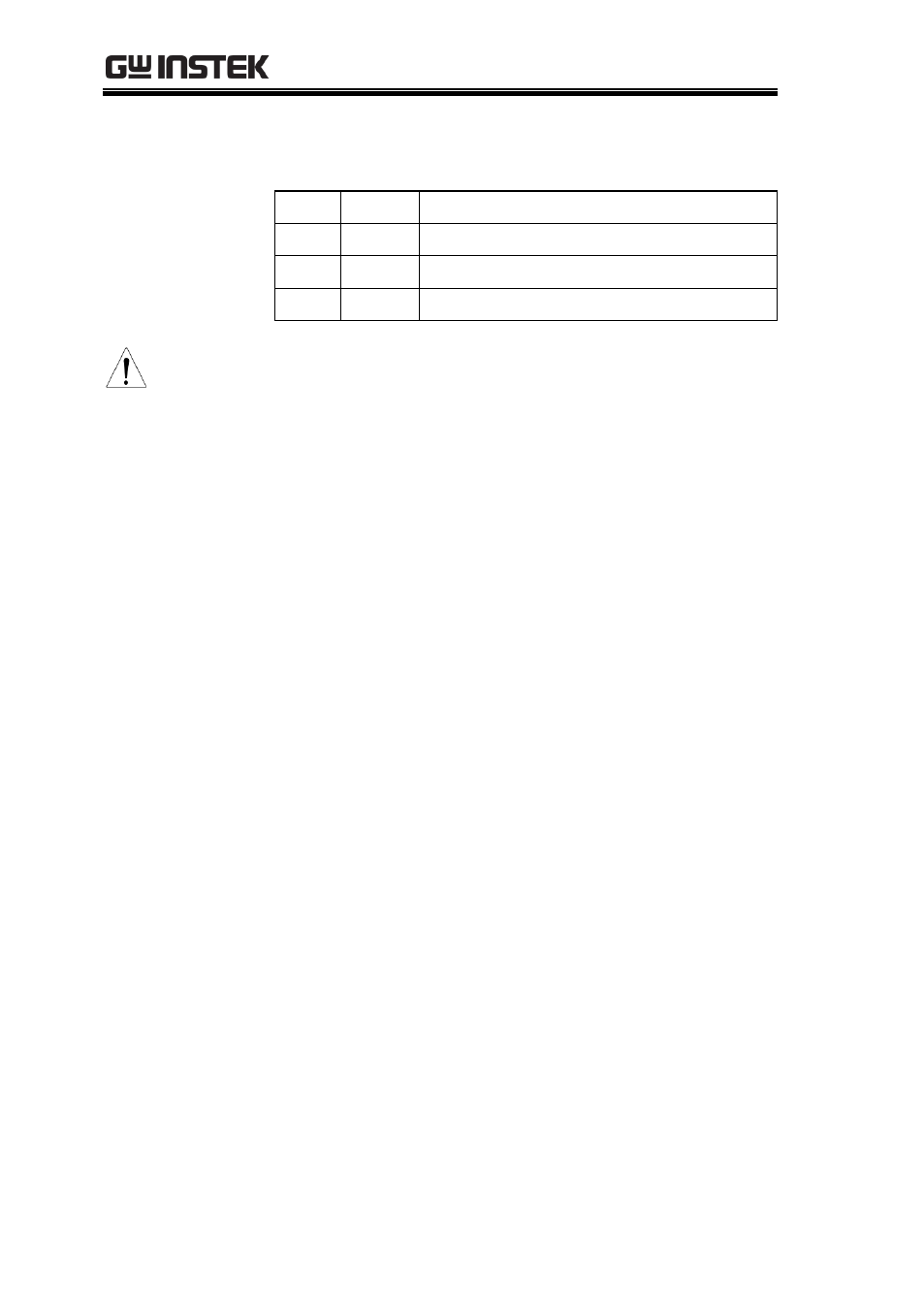

Bit 5

ESB

Standard event status register summary

Bit 4

MAV

Message available

Bit 1

LERR

Local bus execution error

Bit 0

TMO

Local bus time-out

NOTE

An SRQ is issued through the GPIB interface only.

Reading Data from the Status Byte Register and Clearing the

Status Byte Register

Introduction

The content of the status byte register may be read

out from the controller in the following two ways:

Executing the the *STB? query.

When the *STB? query is executed the status of

the MSS bit is returned. No bits of the status

byte are cleared after reading it.

Serial polling.

When serial polling is executed, the status of the

RQS bit (bit 6) is returned. The RQS bit is only

cleared after reading it. It is impossible to read the

MSS bit. It is impossible to clear the status byte

register directly; to clear the status byte register,

you must first clear the associated event registers

that cause the bits of the status byte register to be

set.

When ESB occurs.

When an inquiry is made with the *ESR? query,

the data from the standard event register are

read and all the bits are cleared.

When the *CLS command is received.