Status byte register (stb, sre) – GW Instek PSB-2000 Series User Manual User Manual

Page 133

EXTERNAL CONTROL

133

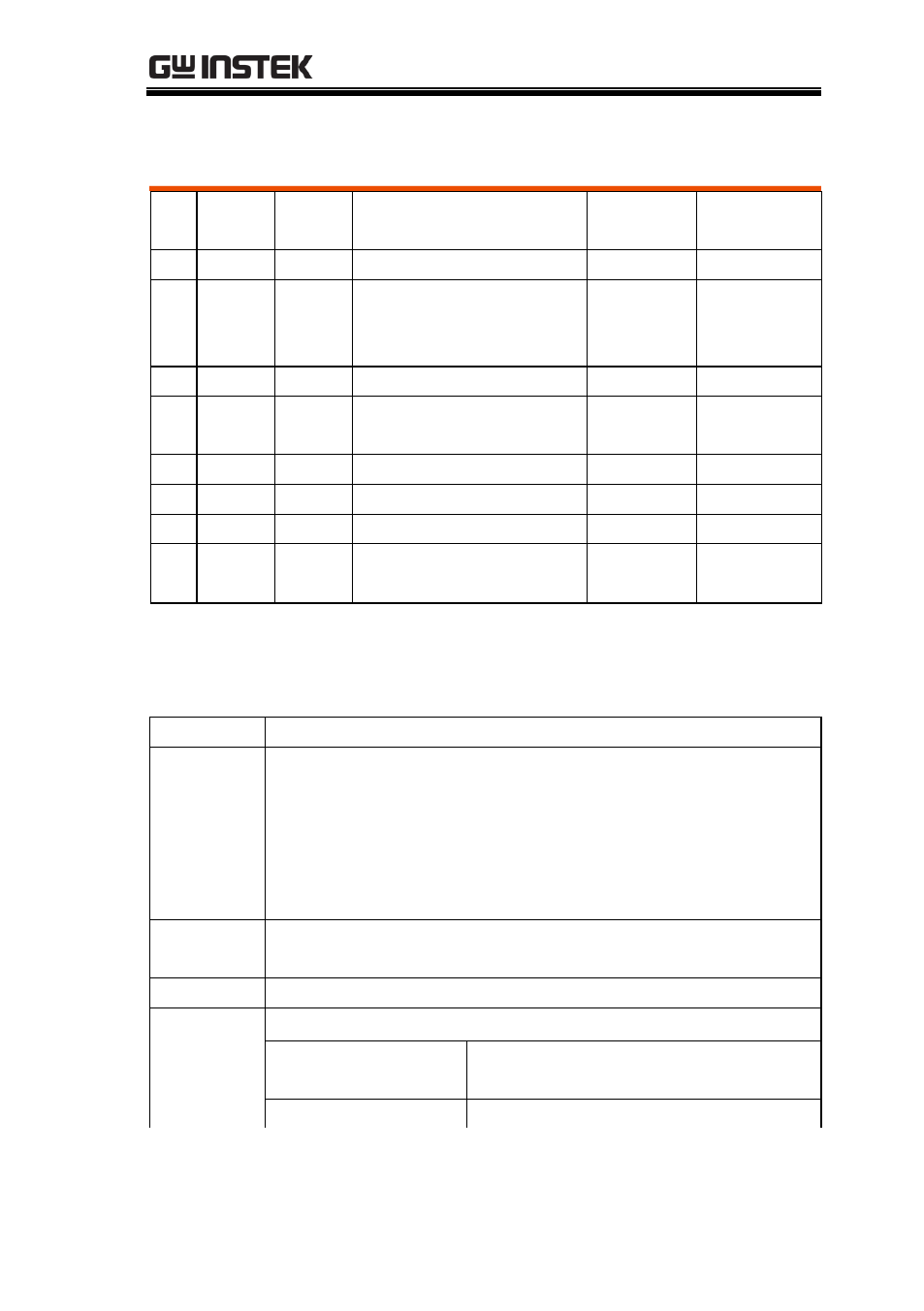

Status Byte Register (STB, SRE)

Bit

Data

Item

Description

Initial STB

value

Initial SRE

value

7

128

0

Unused.

0

0

6

64

SRQ

RQS

MSS

Service request

Message summary

0

0

5

32

ESB

Standard event summary

0

0

4

16

MAV

Output message

available

0

0

3

8

0

Unused.

0

0

2

4

0

Unused.

0

0

1

2

LERR

Local bus error

0

0

0

1

TMO

Local bus

Time out

0

0

Summary

Each bit is masked when it is set to ―0‖. (0 is the

default setting.) A bit is not longer masked when

it is set to 1. Unused bits are set to ―0‖.

Item

Description

SRQ

RQS

MSS

The MSS bit is the summary bit for the status byte register. The

MSS bit is set to 1 when the Boolean AND of the bits in the

status byte register and the bits in the service request enable

register equals 1. The RQS bit is set to 1 when the MSS bit

changes from 0 to 1. The RQS bit is cleared when the MSS bit is

cleared or serial polling is used.

ESB

Indicates that an event occurs in the standard event status

register.

MAV

Indicates that there is a message in the output queue.

*SRE?

Sets or inquires about the service request enable register.

Setting command

*SRE

The

Application example

*SRE 48