Function of the status byte register – GW Instek PSB-2000 Series User Manual User Manual

Page 135

EXTERNAL CONTROL

135

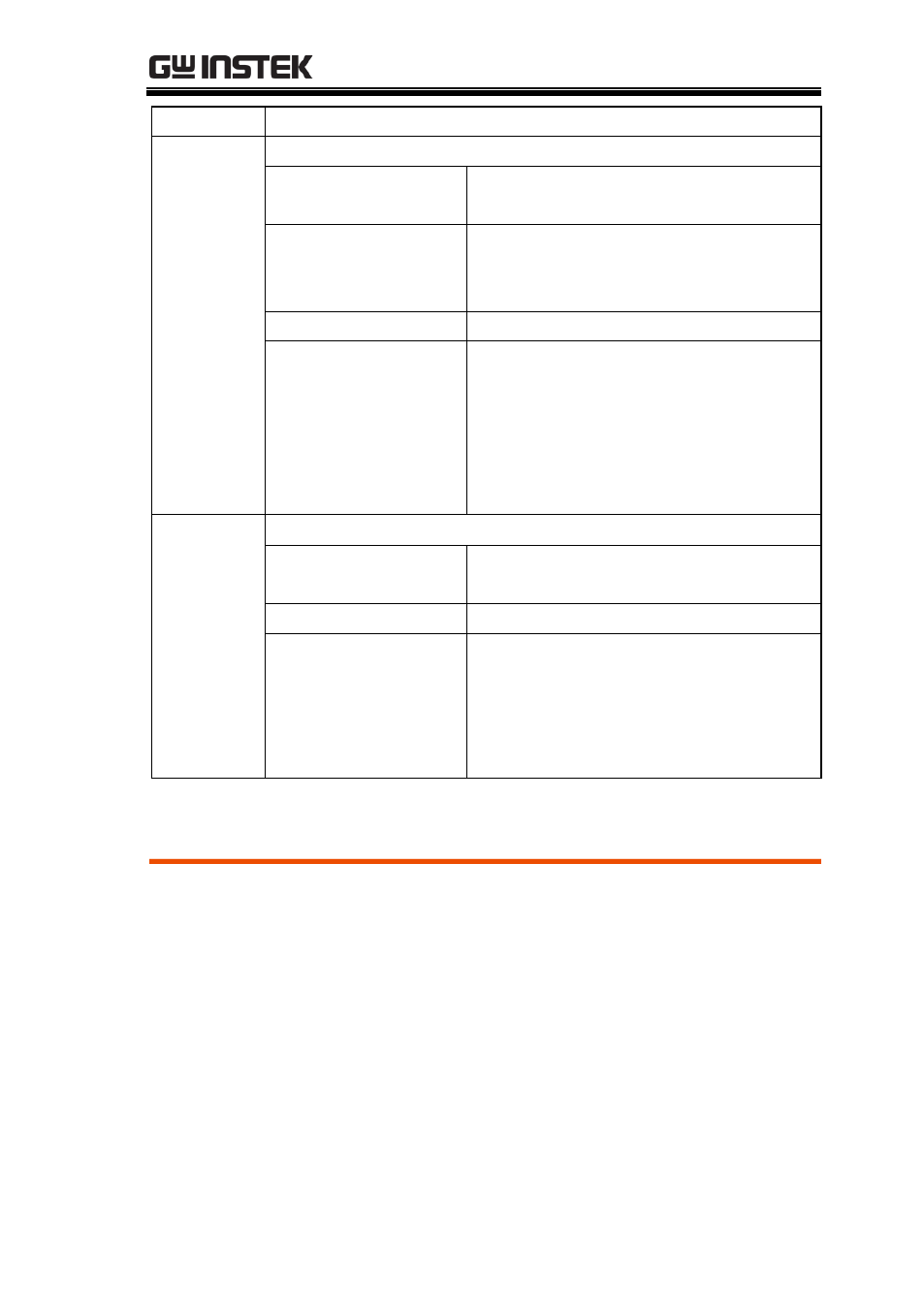

Item

Description

*ESE

Sets or inquires about the standard event status enable register.

Setting command

*ESE

The

Application example

*ESE 48

Enables the CME (bit 5) and EXE (bit 4)

of the Event Status register.

Query command

*ESE?

Response example

48

The masking set with this command

remains valid until the setting is

changed or power is turned off. All bits

are masked (0) when power is turned

on, regardless of the previous setting.

*ESR?

Inquires about the Standard Event Status register.

Setting command

None.

Query only.

Query command

*ESR?

Response example

32

Bit 5 is set indicating that a command

error has occured.

The ESR is cleared after reading the

value.

Function of the Status Byte Register

Introduction

If some event occurs and some bits of the status byte

register are set to 1, bit 6 is set to 1 and a service

request (SRQ) is issued. Four status bits shown

below may possibly be the causes of an SRQ in the

PSB 2000 series power supply unit.

If an execution error occurs, bit 4 of the standard

event status register (ESR) is set to 1. When the

bolean AND of the bits in the ESR and the ESE

equals 1, bit 5 (ESB) of the status byte register is set

to 1. If bit 5 of the service request enable register