Expansion rom base address, Table 4.2 – Avago Technologies LSI53C1020 User Manual

Page 93

PCI Configuration Space Register Descriptions

4-15

Version 2.4

Copyright © 2001–2004 by LSI Logic Corporation. All rights reserved.

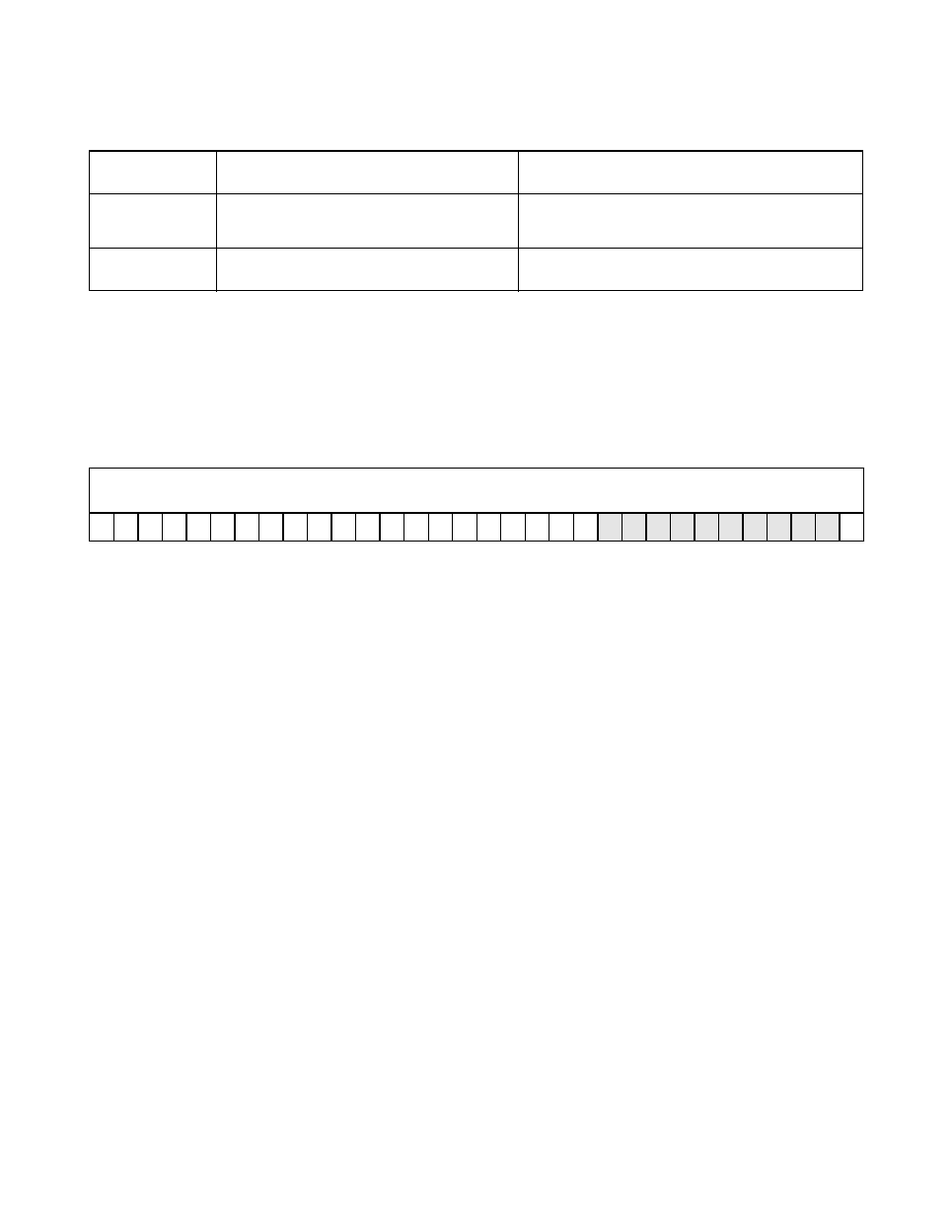

Register: 0x30–0x33

Expansion ROM Base Address

Read/Write

This four-byte register contains the base address and size information for

the expansion ROM.

Expansion ROM Base Address

[31:11]

These bits correspond to the upper 21 bits of the expan-

sion ROM base address. The host system detects the

size of the external memory by first writing 0xFFFFFFFF

to this register and then reading the register back. The

LSI53C1020 responds with zeros in all don’t care loca-

tions. The least significant one (1) that remains repre-

sents the binary version of the external memory size. For

example, to indicate an external memory size of 32

Kbytes, this register returns ones in the upper 17 bits

when written with 0xFFFFFFFF and read back.

Reserved

[10:1]

This field is reserved.

Expansion ROM Enable

0

This bit controls if the device accepts accesses to its

expansion ROM. Setting this bit enables address decod-

ing. Depending on the system configuration, the device

can optionally use an expansion ROM. Note that to

Table 4.2

Subsystem ID Register Download Conditions and Values

MAD[7] State

MAD[10] LOW

MAD[10] HIGH

MAD[7] LOW

= 0xXXXX

Bits [15:0] are downloaded.

1

(Default)

1. The

register returns 0x0000 if the serial EEPROM download fails.

= 0b1XXXXXXXXXXXXXXX

Bits [14:0] are downloaded with Bit [15] set.

2

2. The

register returns 0x8000 if the serial EEPROM download fails.

MAD[7] HIGH

register = 0x1000.

= 0x8000.

31

11 10

1

0

Expansion ROM Base Address

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0