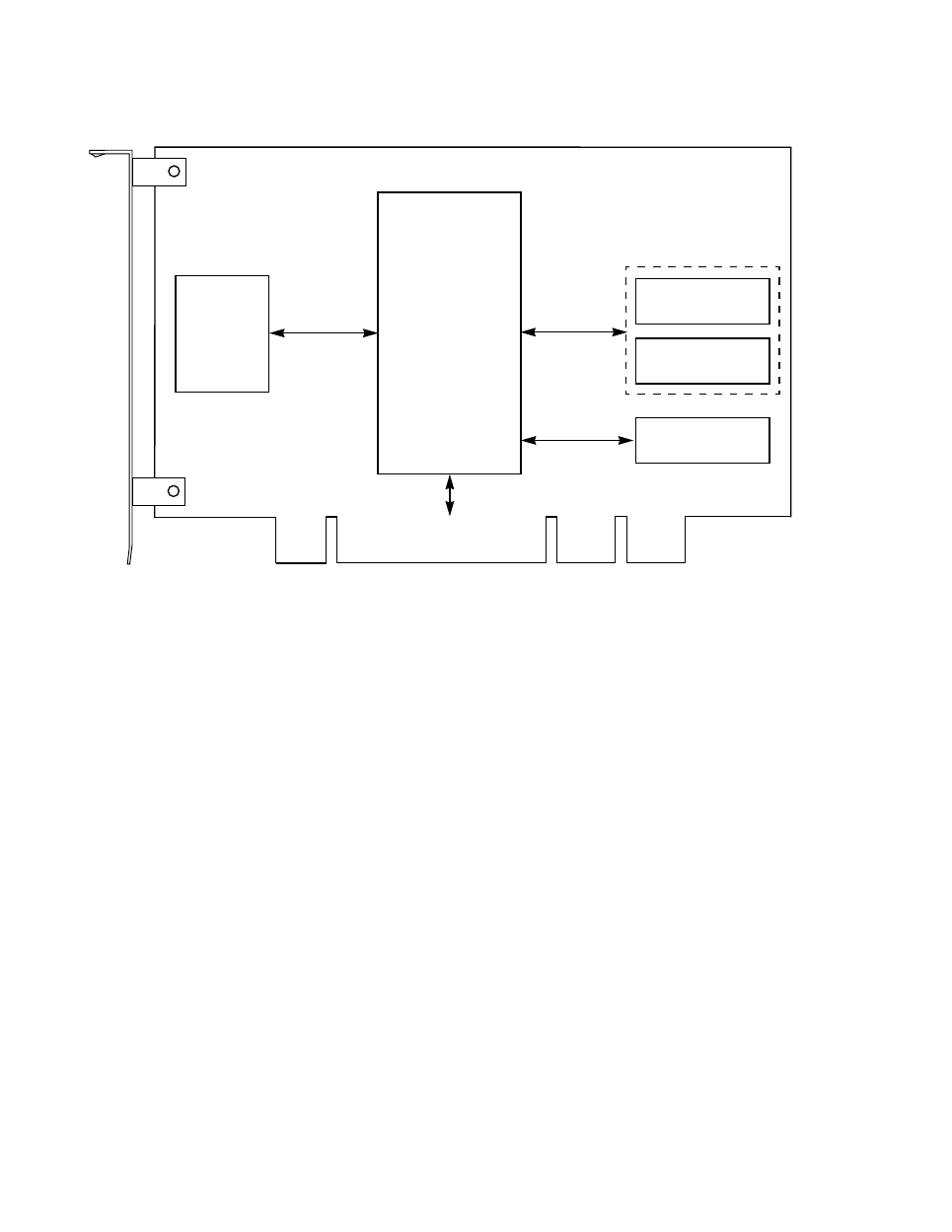

Figure1.1 typical lsi53c1020 board application, Typical lsi53c1020 board application – Avago Technologies LSI53C1020 User Manual

Page 17

General Description

1-3

Version 2.4

Copyright © 2001–2004 by LSI Logic Corporation. All rights reserved.

Figure 1.1

Typical LSI53C1020 Board Application

The LSI53C1020 integrates a high-performance Ultra320 SCSI core and

a 64-bit, 133 MHz PCI-X bus master direct memory access (DMA) core.

The LSI53C1020 employs two ARM966E-S

™

processors to meet the

data transfer flexibility requirements of the Ultra320 SCSI, PCI, and PCI-

X specifications. Separate ARM

®

processors support the SCSI channel

and the PCI/PCI-X interface.

These processors implement the Fusion-MPT™ architecture, a

multithreaded I/O algorithm that supports data transfers between the host

system and SCSI devices with minimal host processor intervention.

Fusion-MPT technology provides an efficient architecture that solves the

protocol overhead problems of previous intelligent and nonintelligent

adapter designs.

LVDlink™ technology is the LSI Logic implementation of Low Voltage

Differential (LVD) SCSI. LVDlink transceivers allow the LSI53C1020 to

perform either Single-Ended (SE) or LVD transfers.

illustrates

a typical LSI53C1020 system application.

Flash ROM

Memory Control

Block

LSI53C1020

64-Bit, 133 MHz

PCI-X to

Ultra320 SCSI

PCI-X Interface

Memory

Address/Data

Bus

Serial Data

Controller

Serial EEPROM

Serial Clock

SCSI Signals

NVSRAM

68-Pin-

Wide SCSI

Connector

and

Terminator