Avago Technologies LSI53C1020 User Manual

Page 148

5-28

Specifications

Version 2.4

Copyright © 2001–2004 by LSI Logic Corporation. All rights reserved.

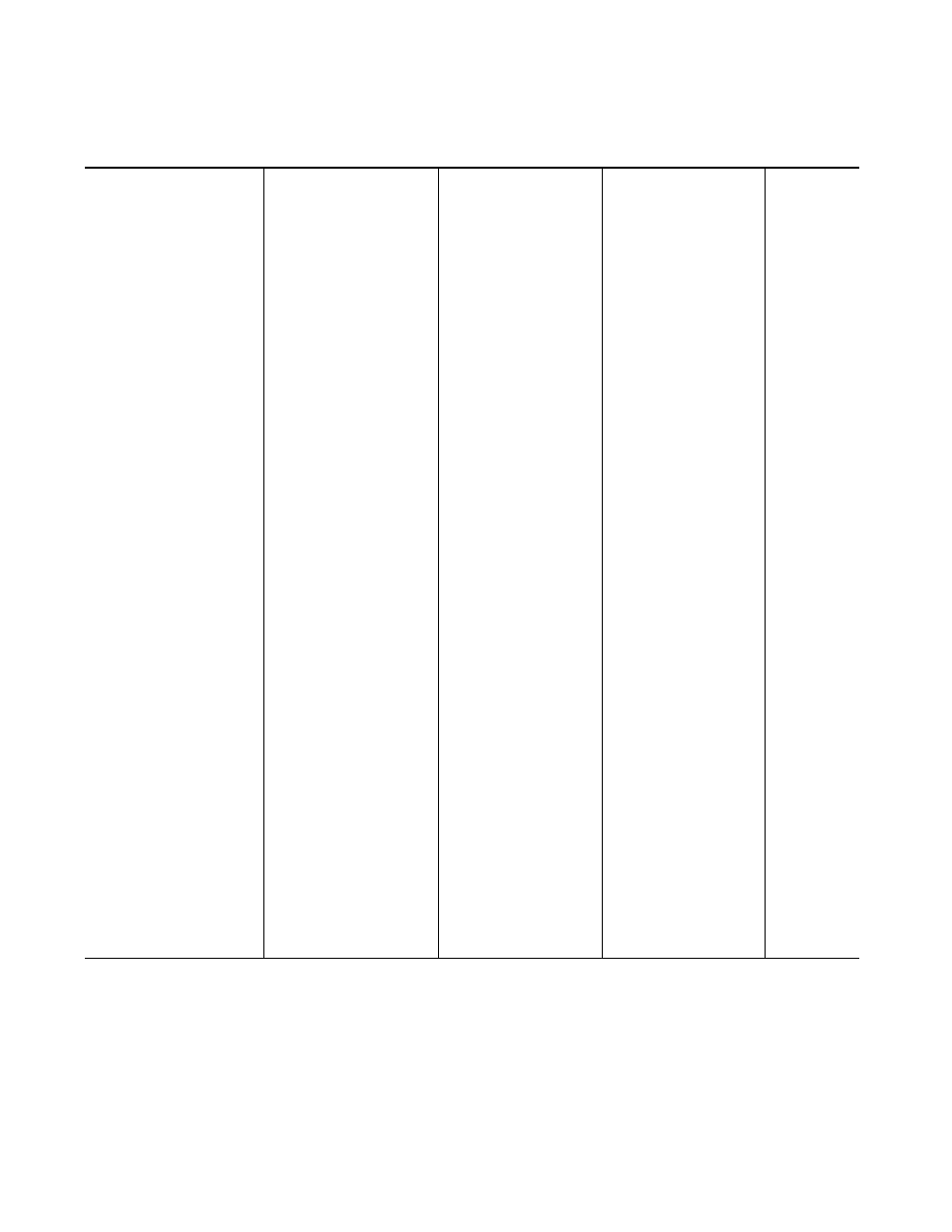

Table 5.22

LSI53C1020A 384-Pin Pinout by Signal Name (Cont.)

Signal

Ball

SD9-

G2

SD9+

G3

SD10-

G4

SD10+

F1

SD11-

F2

SD11+

F3

SD12-

AA4

SD12+

AA2

SD13-

AA1

SD13+

Y3

SD14-

Y4

SD14+

Y2

SD15-

Y1

SD15+

W3

SDP0-

P3

SDP0+

P2

SDP1-

W4

SDP1+

W2

SerialCLK

B17

SerialDATA

C17

SERR/

AF21

SIO-

H2

SIO+

H3

SMSG-

K1

SMSG+

K2

SPARE12

B8

SPARE13

D8

SREQ-

J4

SREQ+

H1

SRST-

L4

SRST+

L3

SSEL-

K3

SSEL+

J1

STOP/

AC20

TCK_CHIP

AE8

TCK_ICE

AE4

TDI_CHIP

AD9

TDI_ICE

AD5

TDO_CHIP AD10

TDO_ICE

AE5

TESTACLK

AE7

TESTHCLK AD7

TM

B6

TMS_CHIP

AF8

TMS_ICE

AF4

TN

C6

TRDY/

AF20

TRST_ICE/

AF5

TST_RST/

AC8

VDD_IO

D6

VDD_IO

D10

VDD_IO

D13

VDD_IO

D14

VDD_IO

D17

VDD_IO

D22

VDD_IO

E23

VDD_IO

F4

VDD_IO

K4

VDD_IO

K23

VDD_IO

N4

VDD_IO

N23

VDD_IO

P4

VDD_IO

P23

VDD_IO

U4

VDD_IO

U23

VDD_IO

AA23

VDD_IO

AB4

VDD_IO

AC6

VDD_IO

AC10

VDD_IO

AC13

VDD_IO

AC14

VDD_IO

AC17

VDD_IO

AC22

VDDA

C5

VDDA

AB24

VDDBIAS

N2

VDDC

A5

VDDC

B19

VDDC

C15

VDDC

D7

VDDC

M2

VDDC

R24

VDDC

U24

VDDC

AC9

VDDC

AD17

VDDC

AE6

VDDC

AF7

VSS_IO

B2

VSS_IO

B25

VSS_IO

C3

VSS_IO

C24

VSS_IO

D4

VSS_IO

D5

VSS_IO

D23

VSS_IO

E4

VSS_IO

L11

VSS_IO

L12

VSS_IO

L13

VSS_IO

L14

VSS_IO

L15

VSS_IO

L16

VSS_IO

M11

VSS_IO

M12

VSS_IO

M13

VSS_IO

M14

VSS_IO

M15

VSS_IO

M16

VSS_IO

N11

VSS_IO

N12

VSS_IO

N13

VSS_IO

N14

VSS_IO

N15

VSS_IO

N16

VSS_IO

P11

VSS_IO

P12

VSS_IO

P13

VSS_IO

P14

VSS_IO

P15

VSS_IO

P16

VSS_IO

R11

VSS_IO

R12

VSS_IO

R13

VSS_IO

R14

VSS_IO

R15

VSS_IO

R16

VSS_IO

T11

VSS_IO

T12

VSS_IO

T13

VSS_IO

T14

VSS_IO

T15

VSS_IO

T16

VSS_IO

AB23

VSS_IO

AC4

VSS_IO

AC5

VSS_IO

AC23

VSS_IO

AD3

VSS_IO

AD24

VSS_IO

AE2

VSS_IO

AE25

VSSA

A4

VSSA

AC26

VSSC

B5

VSSC

B18

VSSC

C7

VSSC

C13

VSSC

C14

VSSC

P1

VSSC

R23

VSSC

T26

VSSC

AC18

VSSC

AD8

VSSC

AE10

VSSC

AF6

ZCR_EN/

G24

Signal

Ball

Signal

Ball

Signal

Ball