5 pci error reporting signals, Table3.5 pci error reporting signals, 6 pci interrupt signals – Avago Technologies LSI53C1020 User Manual

Page 63: Table3.6 pci interrupt signal, Pci error reporting signals, Pci interrupt signals, Pci interrupt signal

PCI Bus Interface Signals

3-7

Version 2.4

Copyright © 2001–2004 by LSI Logic Corporation. All rights reserved.

3.2.5

PCI Error Reporting Signals

describes the PCI Error Reporting signals group.

3.2.6

PCI Interrupt Signals

describes the PCI Interrupt signal.

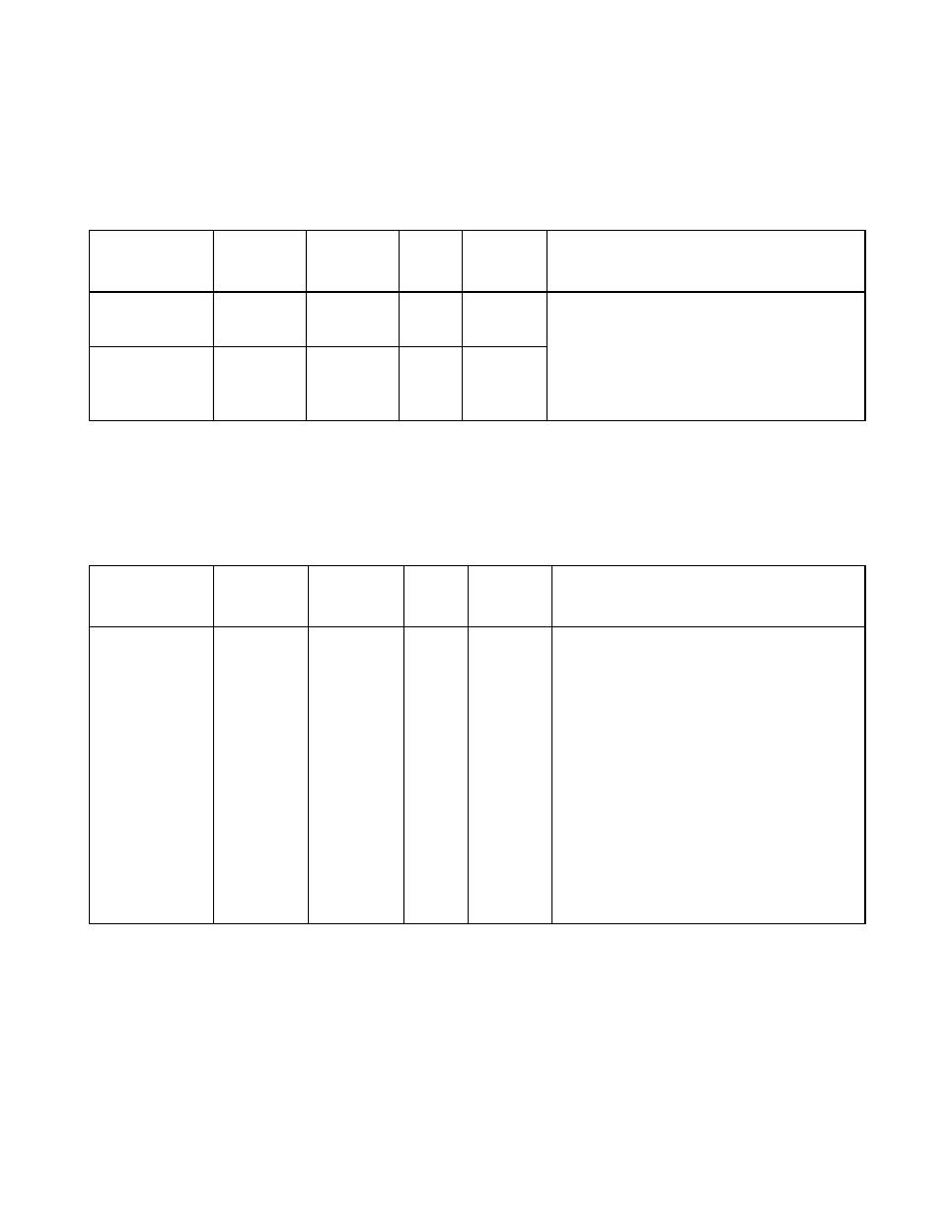

Table 3.5

PCI Error Reporting Signals

Signal Name

456-Ball

Package

384-Ball

Package

Type

Strength Description

PERR/

AE17

AD20

I/O

8 mA

PCI

Refer to the PCI Local Bus Specification

(Version 2.2 for the LSI53C1020, or

Version 2.3 for the LSI53C1020A), and

the PCI-X Addendum to the PCI Local

Bus Specification, Version 1.0a, for

descriptions of these signals.

SERR/

AC17

AF21

I/O

8 mA

PCI

Table 3.6

PCI Interrupt Signal

Signal Name

456-Ball

Package

384-Ball

Package

Type

Strength Description

INTA/

AC8

AE11

O

8 mA

PCI

Refer to the PCI Local Bus Specification

(Version 2.2 for the LSI53C1020, or

Version 2.3 for the LSI53C1020A), and

the PCI-X Addendum to the PCI Local

Bus Specification, Version 1.0a, for this

signal description.

The LSI53C1020 can route the interrupt

signal to INTA/ and/or ALT_INTA/. The

interrupt request routing mode bits, bits

[9:8] in the Host Interrupt Mask register,

control the routing of interrupt signals to

INTA/ and/or ALT_INTA/. Refer to the

register,

for more detailed information.