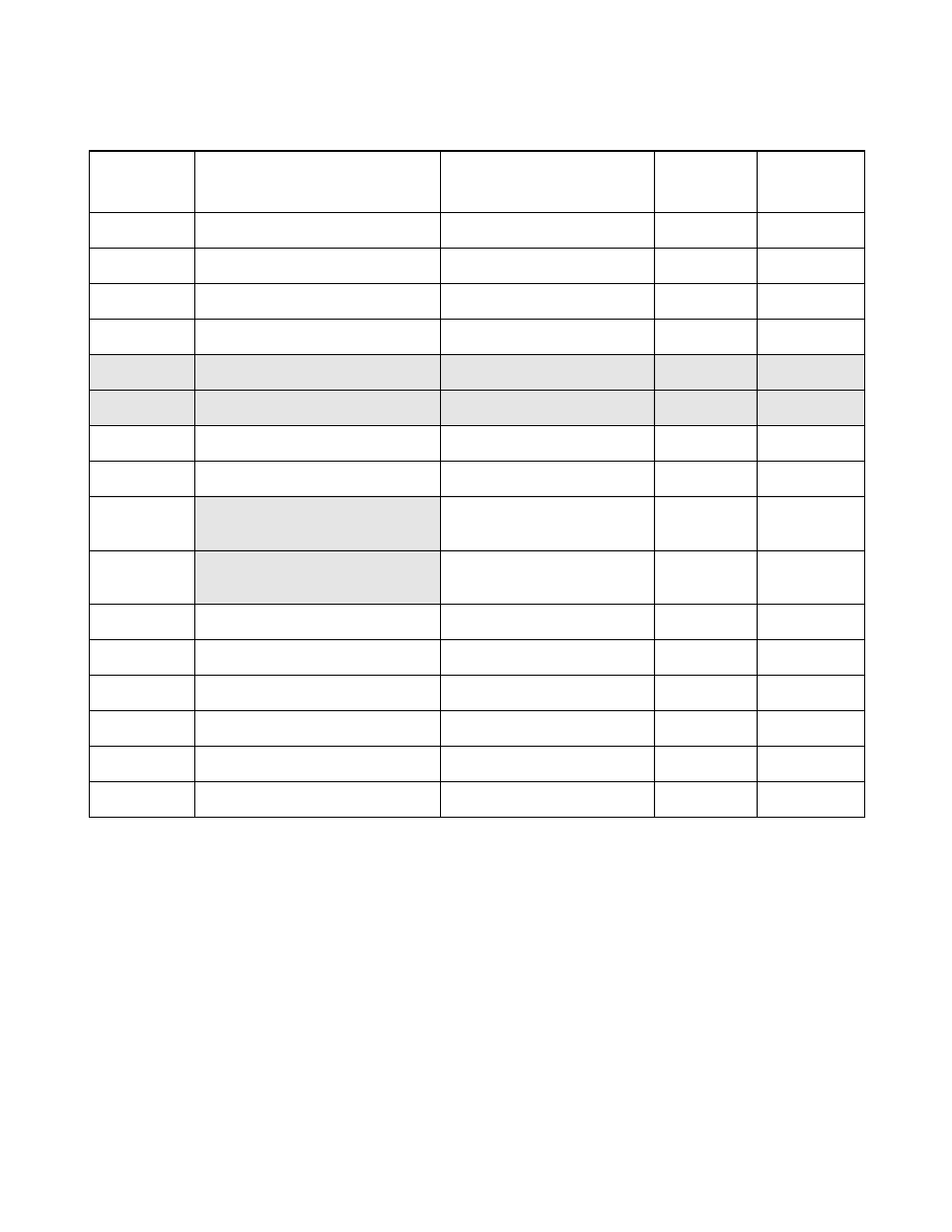

Table2.1 pci/pci-x bus commands and encodings, Pci/pci-x bus commands and encodings, Table 2.1 – Avago Technologies LSI53C1020 User Manual

Page 36

2-10

Functional Description

Version 2.4

Copyright © 2001–2004 by LSI Logic Corporation. All rights reserved.

The following sections describe how the LSI53C1020 implements these

commands.

2.3.2.1

Interrupt Acknowledge Command

The LSI53C1020 ignores this command as a slave and never generates

it as a master.

Table 2.1

PCI/PCI-X Bus Commands and Encodings

1

1. The LSI53C1020 ignores reserved commands as a slave and never generates them as a master.

C_BE[3:0]/

PCI Command

PCI-X Command

Supports

as Master

Supports

as Slave

0b0000

Interrupt Acknowledge

Interrupt Acknowledge

No

No

0b0001

Special Cycle

Special Cycle

No

No

0b0010

I/O Read

I/O Read

Yes

Yes

0b0011

I/O Write

I/O Write

Yes

Yes

0b0100

Reserved

Reserved

N/A

N/A

0b0101

Reserved

Reserved

N/A

N/A

0b0110

Memory Read

Memory Read Dword

Yes

Yes

0b0111

Memory Write

Memory Write

Yes

Yes

0b1000

Reserved

Alias to

Memory Read Block

PCI: N/A

PCI-X: No

PCI: N/A

PCI-X: Yes

0b1001

Reserved

Alias to

Memory Write Block

PCI: N/A

PCI-X: No

PCI: N/A

PCI-X: Yes

0b1010

Configuration Read

Configuration Read

No

Yes

0b1011

Configuration Write

Configuration Write

No

Yes

0b1100

Memory Read Multiple

Split Completion

Yes

Yes

2

2. When acting as a slave in the PCI mode, the LSI53C1020 supports this command as the PCI Mem-

ory Read command.

0b1101

Dual Address Cycle

Dual Address Cycle

Yes

Yes

0b1110

Memory Read Line

Memory Read Block

Yes

Yes

2

0b1111

Memory Write and Invalidate

Memory Write Block

Yes

Yes

3

3. When acting as a slave in the PCI mode, the LSI53C1020 supports this command as the PCI Mem-

ory Write command.