Table3.18 no connect pins, 10 power-on sense pins description, Power-on sense pins description – Avago Technologies LSI53C1020 User Manual

Page 74: No connect pins, Section 3.10, “power-on sense, Section 3.10, “power-on sense pins description

3-18

Signal Description

Version 2.4

Copyright © 2001–2004 by LSI Logic Corporation. All rights reserved.

lists the No Connect pins in both packages:

3.10 Power-On Sense Pins Description

In addition to providing the address/data bus for the external memory

interface, MAD[15:0] and MADP[1:0] provide 18 Power-On Sense pins

that configure global operating conditions within the LSI53C1020. The

MAD[15:0] and MADP[1:0] pins have internal pull-down current sinks and

sense a logical 0 if no pull-up resistor is present on the pin. To program

a particular option, allow the internal pull-down to pull the pin LOW or a

4.7 k

Ω

resistor between the appropriate pin and VDD to pull the pin

HIGH. The LSI53C1020 samples these pins during PCI reset and holds

their values upon the removal of PCI reset.

provides the

MAD Power-On Sense pin configuration options. LSI Logic expects most

configurations to employ the default settings. Provide pull-up options for

all MAD pins.

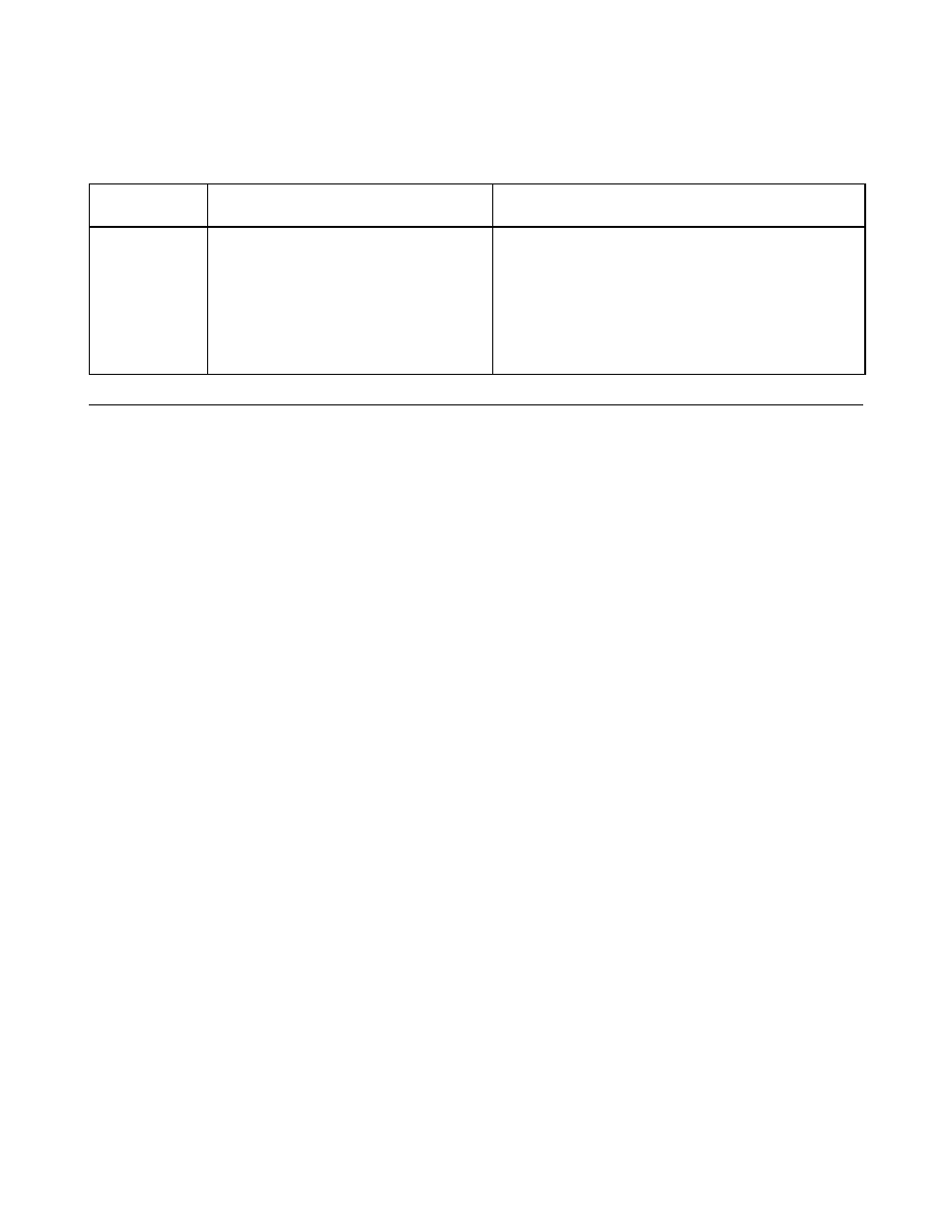

Table 3.18

No Connect Pins

Signal Name 456-Ball Package

384-Ball Package

NC

A3, A4, A7, A8, A11, A12, A15,

A16, A19, A20, A23, B2–B22, C2,

C3, C6, C9, C10, C13, C14, C17,

C18, D4, D5, D6, D8–D19, D21, E3,

E4, E5, E8–E18, E20, F4, F5, G5,

G24, K23, T3, W24, AB9, AC2, AE7

A2, A3, A24, A25, B1, B3, B23, B24, B26, C1,

C2, C4, C8, C23, C25, C26, D1, D2, D3, D24,

D25, D26, E2, E3, E24, E25, E26, F23–F26,

G23, G25, G26, U26, AA3, AB1, AB2, AB3,

AC1, AC2, AC3, AC24, AC25, AD1, AD2, AD22,

AD23, AD25, AD26, AE1, AE3, AE23, AE24,

AE26, AF2, AF9, AF24, AF25