6 serial eeprom interface, Serial eeprom interface, Pci configuration record in serial eeprom – Avago Technologies LSI53C1020 User Manual

Page 53: Section 2.6, “serial eeprom interface, Section 2.6, “serial eeprom

Serial EEPROM Interface

2-27

Version 2.4

Copyright © 2001–2004 by LSI Logic Corporation. All rights reserved.

When using an NVSRAM, pull the MAD[3] Power-On Sense pin HIGH

during board boot-up. This configures the external memory interface as

an NVSRAM interface. During operation, RAMCE/ selects the NVSRAM

when MAD[3] is pulled HIGH.

2.6

Serial EEPROM Interface

The nonvolatile external serial EEPROM stores configuration fields for

the LSI53C1020. The serial EEPROM contains fields for the Subsystem

ID, Subsystem Vendor ID, and the size of the PCI Diagnostic Memory

Space. The LSI53C1020 must establish each of these parameters prior

to reading system BIOS and loading the PCI Configuration Space

registers. The power-on option settings enable the download of PCI

configuration data from the serial EEPROM. For more information on the

setting of the power-on options, refer to

.

A 2-wire serial interface provides the connection to the serial EEPROM.

During initialization, the firmware checks if a serial EEPROM exists.

Firmware uses the checksum byte to determine if the configuration held

in the serial EEPROM is valid. If the checksum fails, the firmware checks

for a valid NVData signature. If a valid NVData signature is found, the

firmware individually checksums each persistent configuration page to

find the invalid page or pages.

provides the structure of the

configuration record in the serial EEPROM.

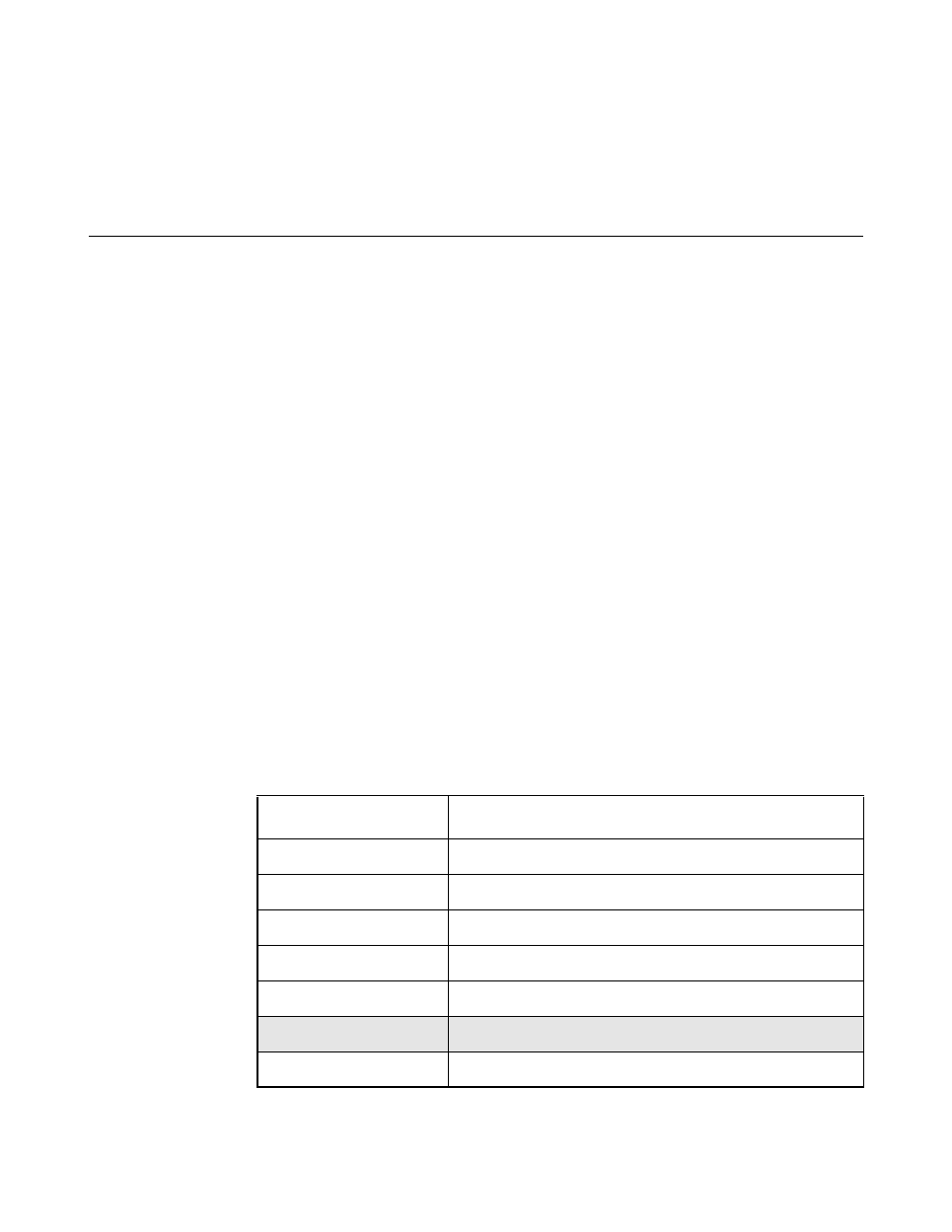

Table 2.5

PCI Configuration Record in Serial EEPROM

EEPROM Address

Configuration Data

0x00

, bits [7:0]

0x01

, bits [15:8]

0x02

, bits [7:0]

0x03

, bits [15:8]

0x04

PCI Diagnostic Memory Size

0x05–0x09

Reserved

0x0A

Checksum