Avago Technologies LSI53C1020 User Manual

Page 5

Preface

v

Version 2.4

Copyright © 2001–2004 by LSI Logic Corporation. All rights reserved.

Conventions Used in This Manual

The first time a word or phrase is defined in this manual, it is italicized.

The word assert means to drive a signal true or active. The word

deassert means to drive a signal false or inactive. Signals that are active

LOW end with a “/.”

Hexadecimal numbers are indicated by the prefix “0x” —for example,

0x32CF. Binary numbers are indicated by the prefix “0b” —for example,

0b0011.0010.1100.1111.

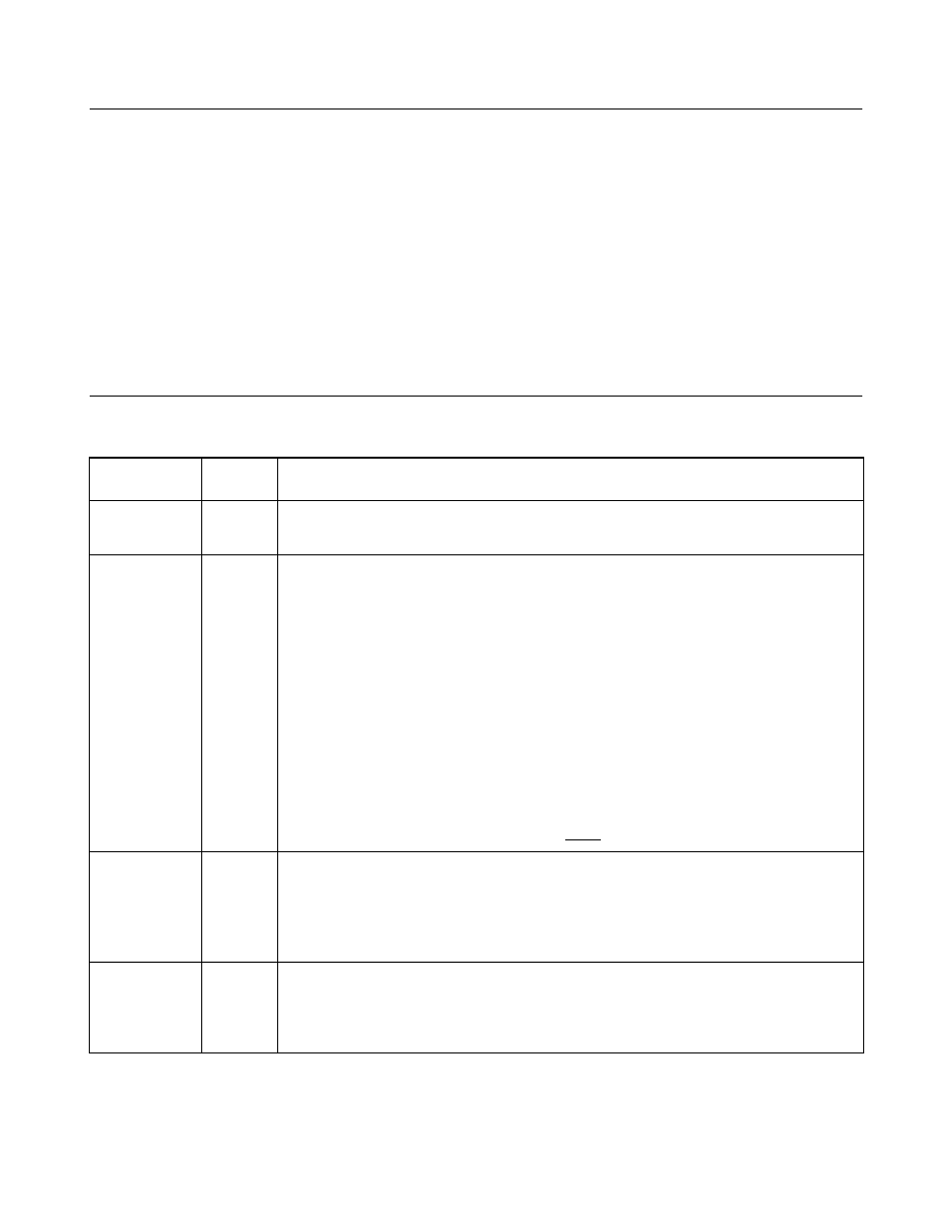

Revision History

Revision

Date

Remarks

v2.4

2/2004

Corrected PCI support information and package/pin compatibility information

in Chapter 1.

v2.3

2/2004

Added 384-pin entries to signal description tables in Chapter 3.

Corrected and updated pin/signal names and ball assignments throughout

the document. Verified that this data is now consistent for the 384-pin and

456-pin packages.

Added a statement that LSI53C1020A controller supports v2.3 of the PCI

spec.

Added descriptions of the Interrupt Disable and Interrupt Status bits to the

PCI Command Register and PCI Status Register sections in Chapter 4 and

noted that the LSI53C1020A controller supports these functions.

Deleted this sentence from section 2.7: “LSI53C1020 based designs do not

use the M66EN pin to determine the PCI bus speed.” (The sentence was not

relevant, since the chip has no M66EN pin.)

Made this correction in description of Diagnostic Read/Write Address regis-

ter: “The address increments by a dword whenever the host system

accesses the Diagnostic Read/Write Data register.”

v2.2

12/2003 Updated references to Integrated RAID throughout the document.

Corrected SCSI clock, SCLK LOW, and SCLK HIGH timings in Table 5.13.

Added pinout information for 448 EPBGA and 384 EPBGA packages of the

LSI53C1020A chip. Edited descriptions of Request Queue and Reply Queue

registers (formerly called “Request FIFO” and “Reply FIFO,” respectively).

v2.1

6/2003

Updated the external memory timing diagrams.

Updated the default Subsystem ID value.

Updated the ZCR behavior description.

Updated the Multi-ICE test interface description.