Table3.19 mad power-on sense pin options, Mad power-on sense pin options – Avago Technologies LSI53C1020 User Manual

Page 75

Power-On Sense Pins Description

3-19

Version 2.4

Copyright © 2001–2004 by LSI Logic Corporation. All rights reserved.

•

MADP[1], Reserved.

•

MADP[0], PCI-X Mode – By default, internal logic pulls this pin LOW

to enable the PCI-X mode on the LSI53C1020. Pulling this pin HIGH

disables the PCI-X mode on the LSI53C1020. Pull this pin HIGH

when the host board does not support the PCI-X mode. The setting

of this pin must coincide with the setting of the PCI_CAP pin on the

host board. When the PCI-X mode is disabled, the PCI-X extended

capabilities register structure is not visible in PCI Configuration

Space.

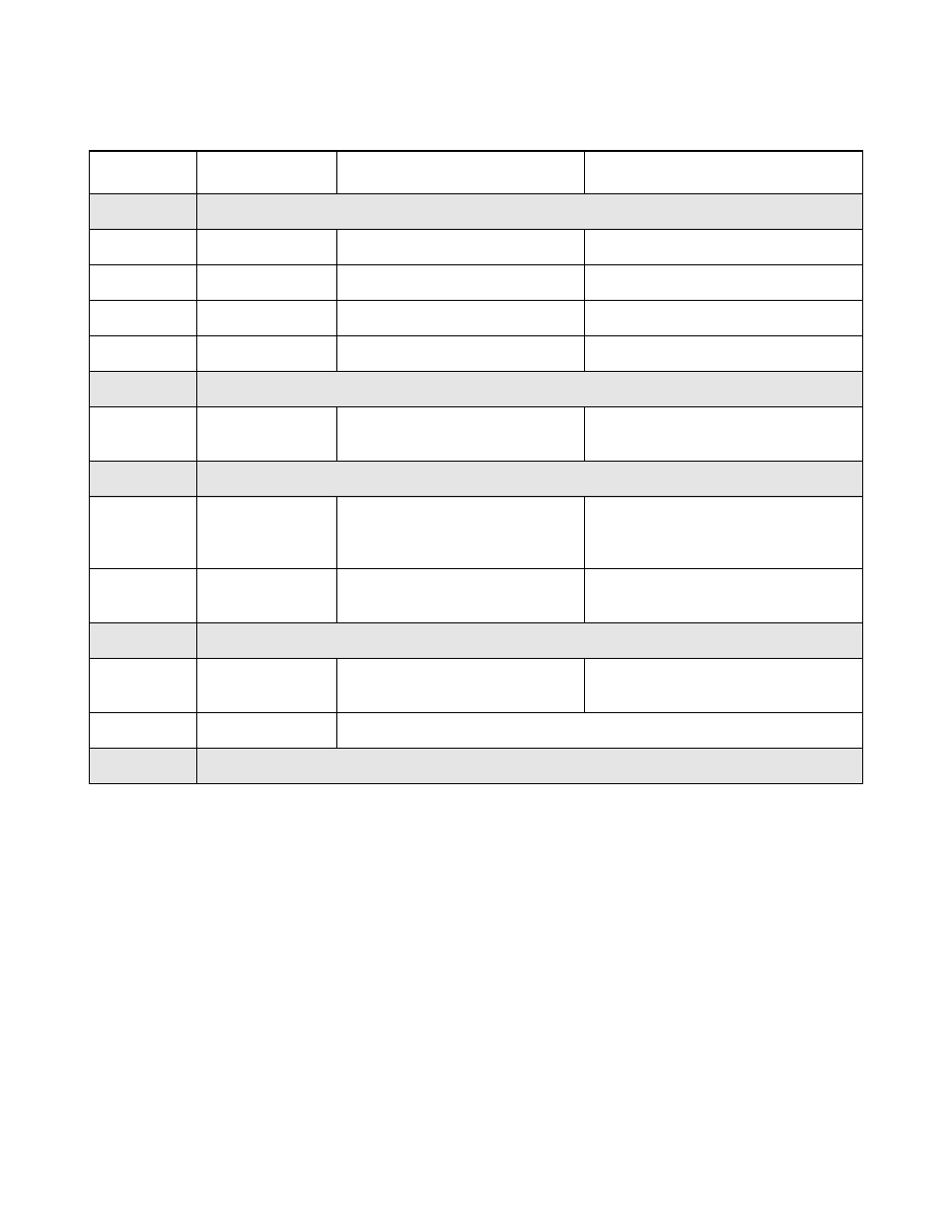

Table 3.19

MAD Power-On Sense Pin Options

MAD Pin

Function

Pulled-Down (Default)

Pulled-Up

MADP[1]

Reserved

MADP[0]

PCI-X mode

Enables the PCI-X mode.

Disables the PCI-X mode.

MAD[15]

133 MHz PCI-X

Enables 133 MHz PCI-X mode. Disables the 133 MHz PCI-X mode.

MAD[14]

64-bit PCI

Configures a 64-bit PCI bus.

Configures a 32-bit PCI bus.

MAD[13]

66 MHz PCI

Enables the 66 MHz PCI mode. Disables the 66 MHz PCI mode.

MAD[12:11]

Reserved

MAD[10]

ID Control

Has no effect.

Sets bit [15] of the

register to 0b1.

MAD[9:8]

Reserved

MAD[7]

Serial EEPROM

Download

Enable

Enables the download of the

PCI configuration information

from the serial EEPROM.

Disables the download of the PCI

configuration information from the

serial EEPROM.

MAD[6]

IOP Boot

Enable

Enables the IOP boot process. Disables the IOP boot process.

MAD[5:4]

Reserved

MAD[3]

NVSRAM Select Has no effect.

Configures the LSI53C1020 to

support an NVSRAM.

MAD[2:1]

Flash ROM Size Configures the Flash ROM Size according to

.

MAD[0]

Reserved