2 i/o space and memory space register descriptions, Table4.3 pci i/o space address map, I/o space and memory space register descriptions – Avago Technologies LSI53C1020 User Manual

Page 110: Pci i/o space address map

4-32

PCI Host Register Description

Version 2.4

Copyright © 2001–2004 by LSI Logic Corporation. All rights reserved.

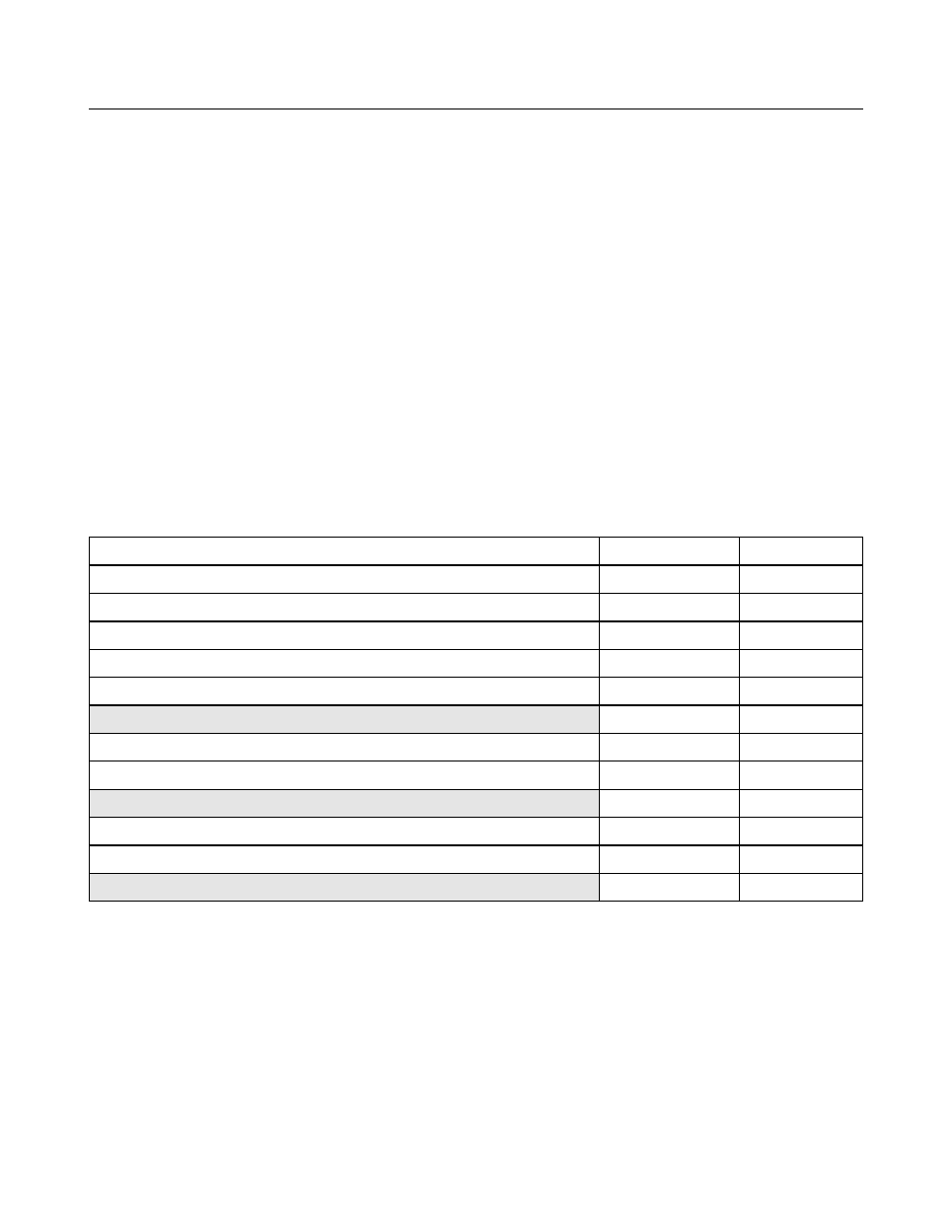

4.2

I/O Space and Memory Space Register Descriptions

This section describes the host interface registers in the PCI I/O Space

and PCI Memory Space. These address spaces contain the Fusion-MPT

interface register set. PCI Memory Space [0] and PCI Memory Space [1]

form the PCI Memory Space. PCI Memory [0] supports normal memory

accesses while PCI Memory Space [1] supports diagnostic memory

accesses. For all registers except the

and

registers, access the address offset

through either PCI I/O Space or PCI Memory Space [0]. Access to the

and

registers is only through PCI I/O Space.

defines the PCI I/O Space address map.

Table 4.3

PCI I/O Space Address Map

31

0

Offset

Page

0x0000

0x0004

0x0008

0x000C

0x0010

0x0014

Reserved

0x0018–0x002F

–

0x0030

0x0034

Reserved

0x0038–0x003F

–

0x0040

0x0044

Reserved

0x0048–0x007F

–