Pci-x next pointer, Pci-x command, Register: 0xxx – Avago Technologies LSI53C1020 User Manual

Page 105

PCI Configuration Space Register Descriptions

4-27

Version 2.4

Copyright © 2001–2004 by LSI Logic Corporation. All rights reserved.

Register: 0xXX

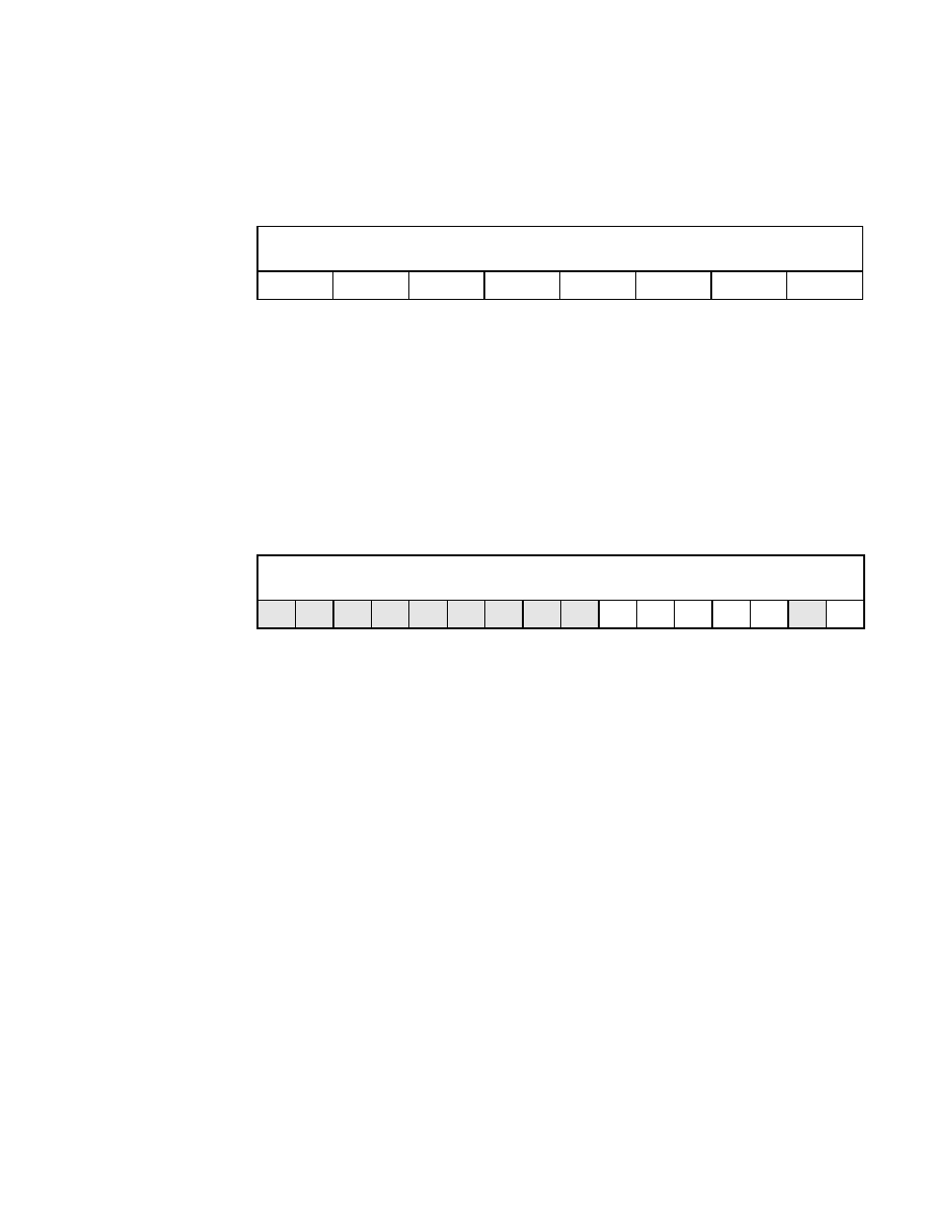

PCI-X Next Pointer

Read Only

PCI-X Next Pointer

[7:0]

This 8-bit register points to the next item in the device’s

capabilities list. The value of this register varies according

to system configuration.

Register: 0xXX

PCI-X Command

Read/Write

Reserved

[15:7]

This field is reserved.

Maximum Outstanding Split Transactions

[6:4]

These bits indicate the maximum number of split transac-

tions the LSI53C1020 can have outstanding at one time.

The LSI53C1020 uses the most recent value of this reg-

ister each time it prepares a new sequence. Note that if

the LSI53C1020 prepares a sequence before the setting

of this field changes, the PCI function initiates the pre-

pared sequence with the previous setting. The following

table provides the bit encodings for this field.

7

0

PCI-X Next Pointer

X

X

X

X

X

X

X

X

15

7

6

4

3

2

1

0

PCI-X Command

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0