Figure5.8 nvsram read cycle, Nvsram read cycle – Avago Technologies LSI53C1020 User Manual

Page 133

External Memory Timing Diagrams

5-13

Version 2.4

Copyright © 2001–2004 by LSI Logic Corporation. All rights reserved.

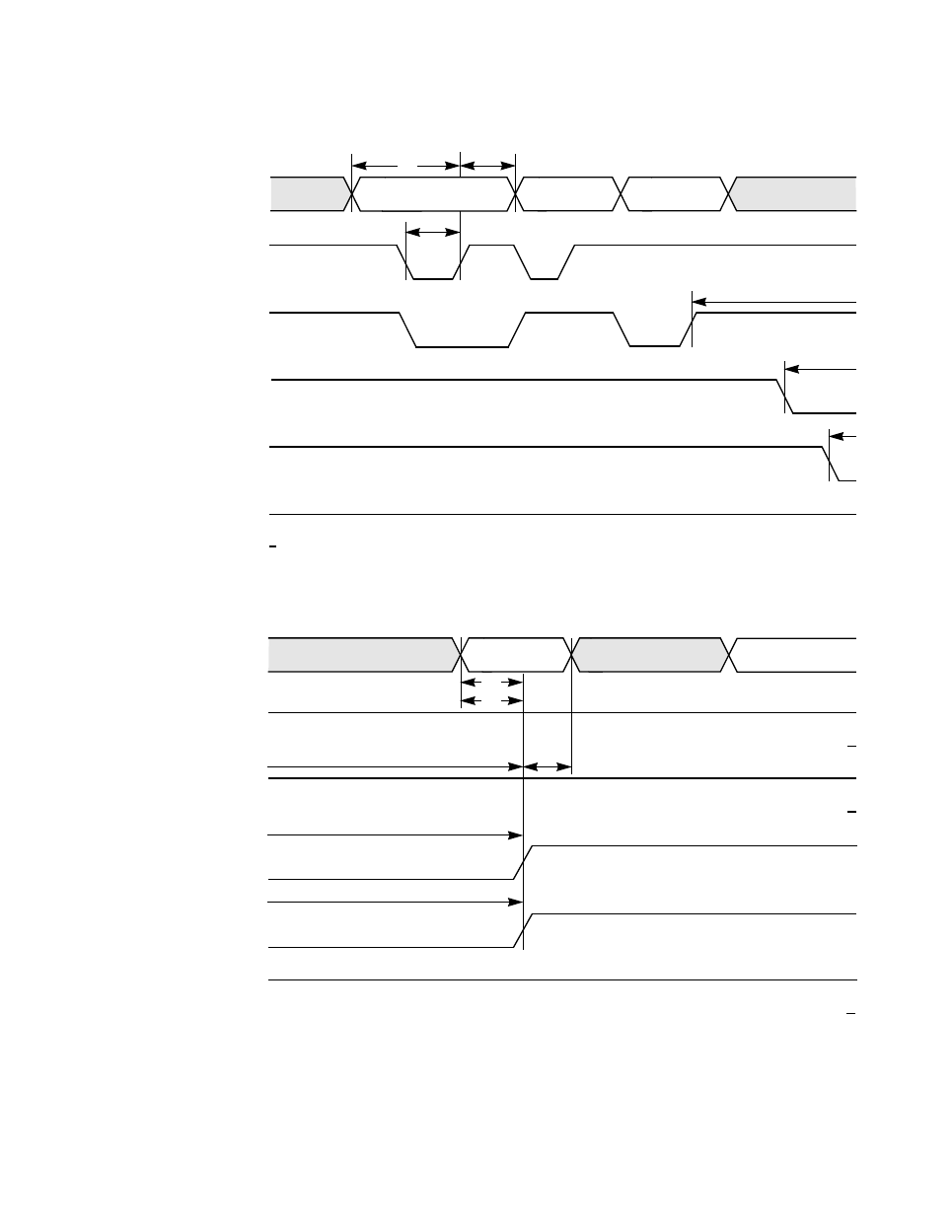

Figure 5.8

NVSRAM Read Cycle

Figure 5.8

NVSRAM Read Cycle (Cont.)

Data Driven by NVSRAM)

MAD Bus

(Addr Driven by LSI53C1020;

High Order Address

Middle Order

Address

FLSHALE1/

(Driven by LSI53C1020)

FLSHALE0/

(Driven by LSI53C1020)

RAMCE/

(Driven by LSI53C1020)

RAMOE/

(Driven by LSI53C1020)

RAMWE0/

(Driven by LSI53C1020)

t

3

t

1

t

2

t

4

t

5

t

6

Low Order

Address

Data Driven by NVSRAM)

MAD Bus

(Addr Driven by LSI53C1020;

FLSHALE1/

(Driven by LSI53C1020)

FLSHALE0/

(Driven by LSI53C1020)

RAMCE/

(Driven by LSI53C1020)

RAMOE/

(Driven by LSI53C1020)

RAMWE0/

(Driven by LSI53C1020)

t

4

t

9

t

5

Valid

t

6

t

8

t

7

Read Data

This manual is related to the following products: