Comtech EF Data C5 User Manual

Page 273

C5/K1/K3 Integrated Satellite Terminal System

Options

Rev. 0

A–29

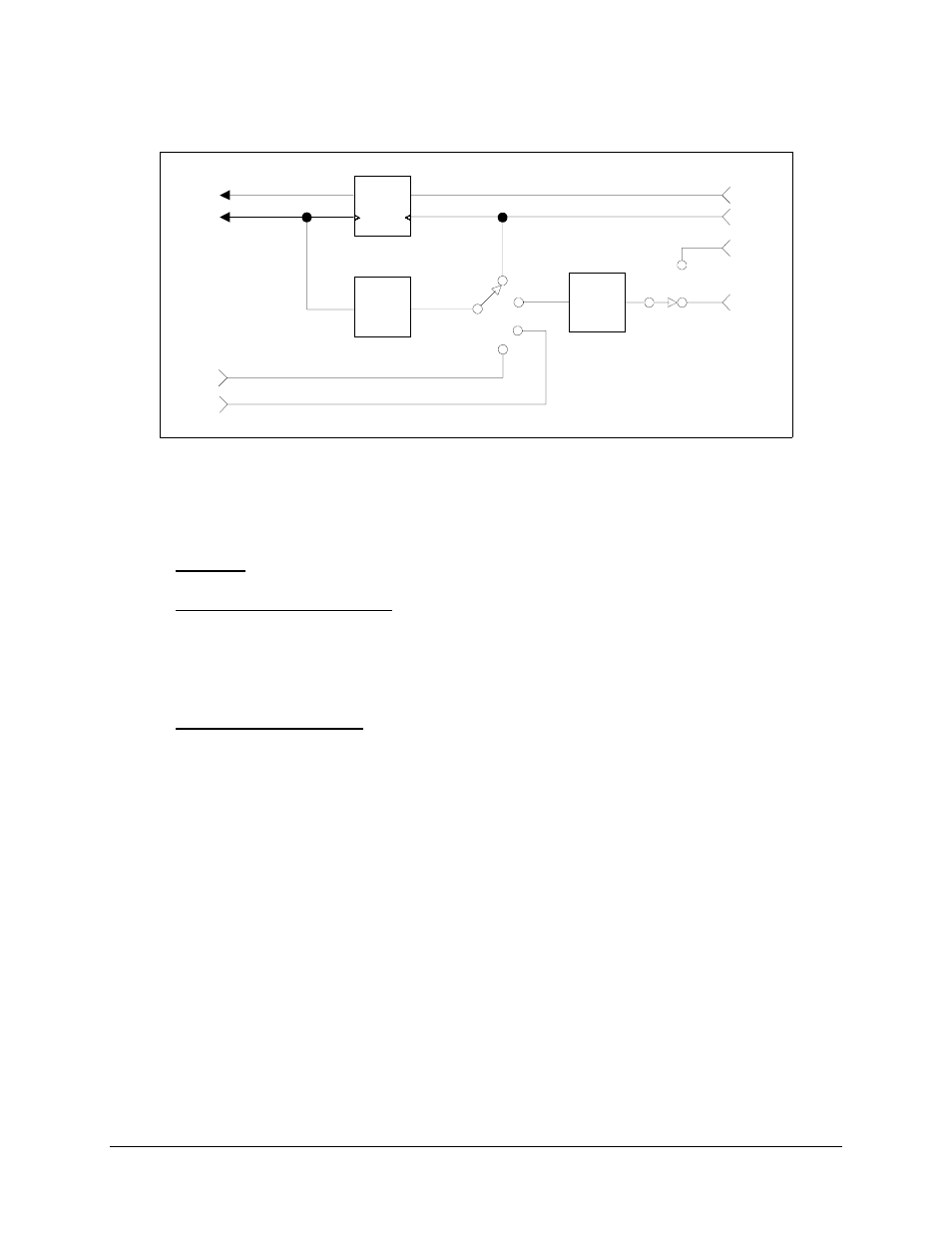

BUF

PLL

SAT

INT

RXD

MC

EXT

TERR

TT

RT

DDS

EXT

REF

INT

RXD

RXC

Note: PLL will be bypassed when the receive data rate is set to the transmit data rate. This will

disable the Asymmetrical Mode.

Figure A-7. Receive Section of the Asymmetrical Loop Timing Block Diagram

Example:

Master/Slave Clocking Setup:

1. Master site has a 10 MHz clock that is needed as the clock source.

2. Unequal data rates: 4.096 Mbit/s and 2.152 Mbit/s (numbers divisible by 8).

Master Site Option No. 1:

1. Set Configuration/Modulator/ Modem Reference to EXT 10 MHz.

2. Set Configuration/Interface/TX Clock Source to SCT (Internal).

Note: The SCT clock is slaved off the 10 MHz input. The 10 MHz reference should

be placed into CP3 of the modem.

3. Set Configuration/Interface/ Buffer Clock to SCT (Internal).