NEC PD17062 User Manual

Page 96

96

µ

PD17062

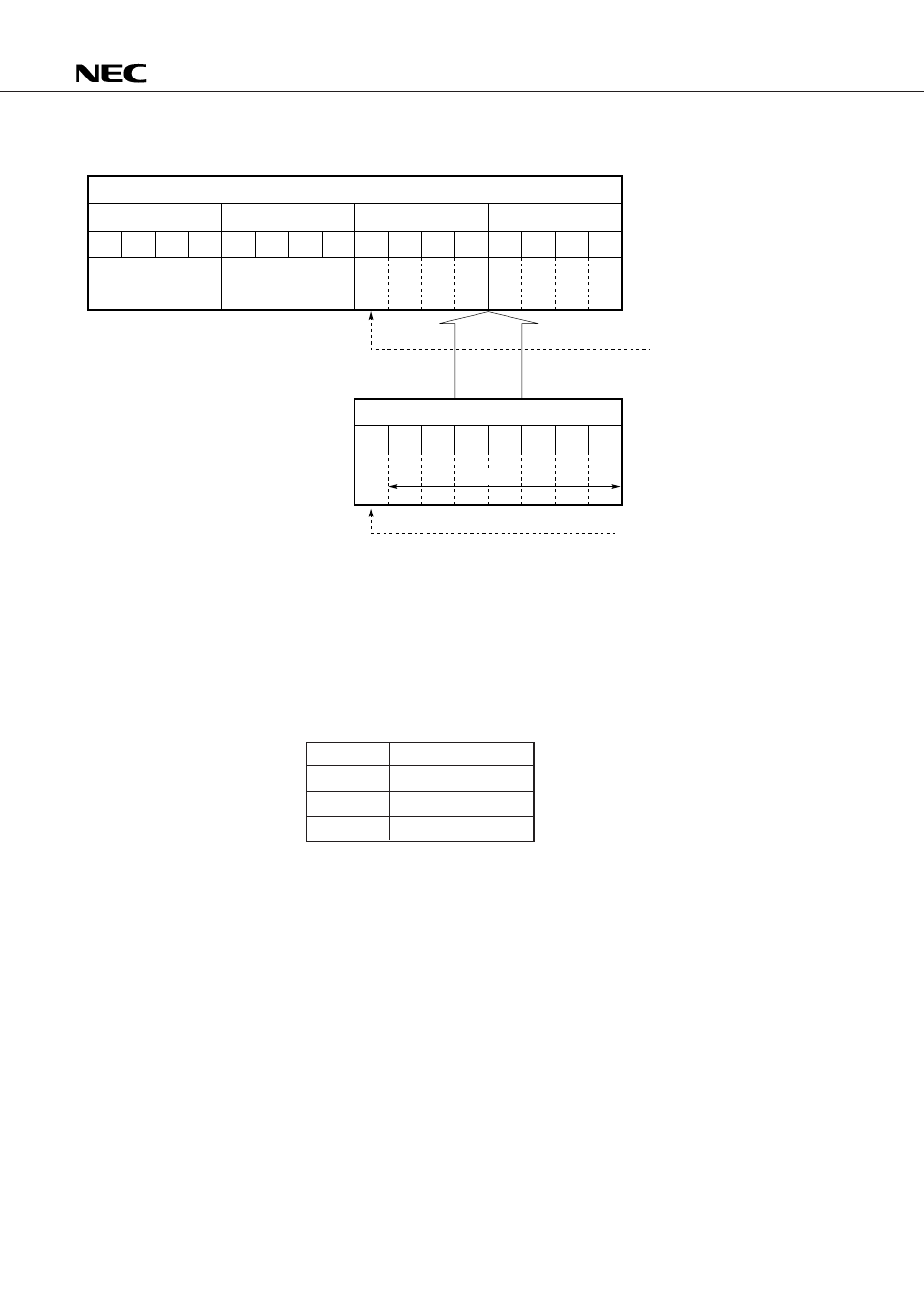

Example 2. GET instruction

When the 8-bit data of a peripheral register is read, the value of the eight high-order bits (DBF3 and DBF2)

of the data register does not change.

Of the 8-bit data of the data register, each bit that is not a valid peripheral register bit becomes 0 or

unpredictable. Whether the bit becomes 0 or unpredictable is decided in advance for each peripheral register.

10.4.3 State at Peripheral Register Reset

The valid bits of each peripheral register are reset as follows:

DBF3

DBF2

DBF1

DBF0

b

15

b

14

b

13

b

12

b

11

b

10

b

9

b

8

b

7

b

6

b

5

b

4

b

3

b

2

b

1

b

0

Peripheral register

b

7

b

6

b

5

b

4

b

3

b

2

b

1

b

0

GET

Data buffer

8

Don't care

Don't care

0 or unpredictable

0 or unpredictable

The value of the

peripheral register

is read without alteration.

Valid bits

Reset

Valid bit state

Power-on

Unpredictable

Clock-stop

Previous state held

CE

Previous state held