Horizontal sync signal counter, 1 horizontal sync signal counter configuration – NEC PD17062 User Manual

Page 274

274

µ

PD17062

21. HORIZONTAL SYNC SIGNAL COUNTER

21.1 HORIZONTAL SYNC SIGNAL COUNTER CONFIGURATION

The horizontal sync signal counter counts the frequency of a horizontal sync signal for TV or similar

equipment. When a TV broadcasting signal is received, a prescribed horizontal sync signal is output. Using

this fact, the horizontal sync signal counter checks whether there is a broadcast station at a particular

frequency.

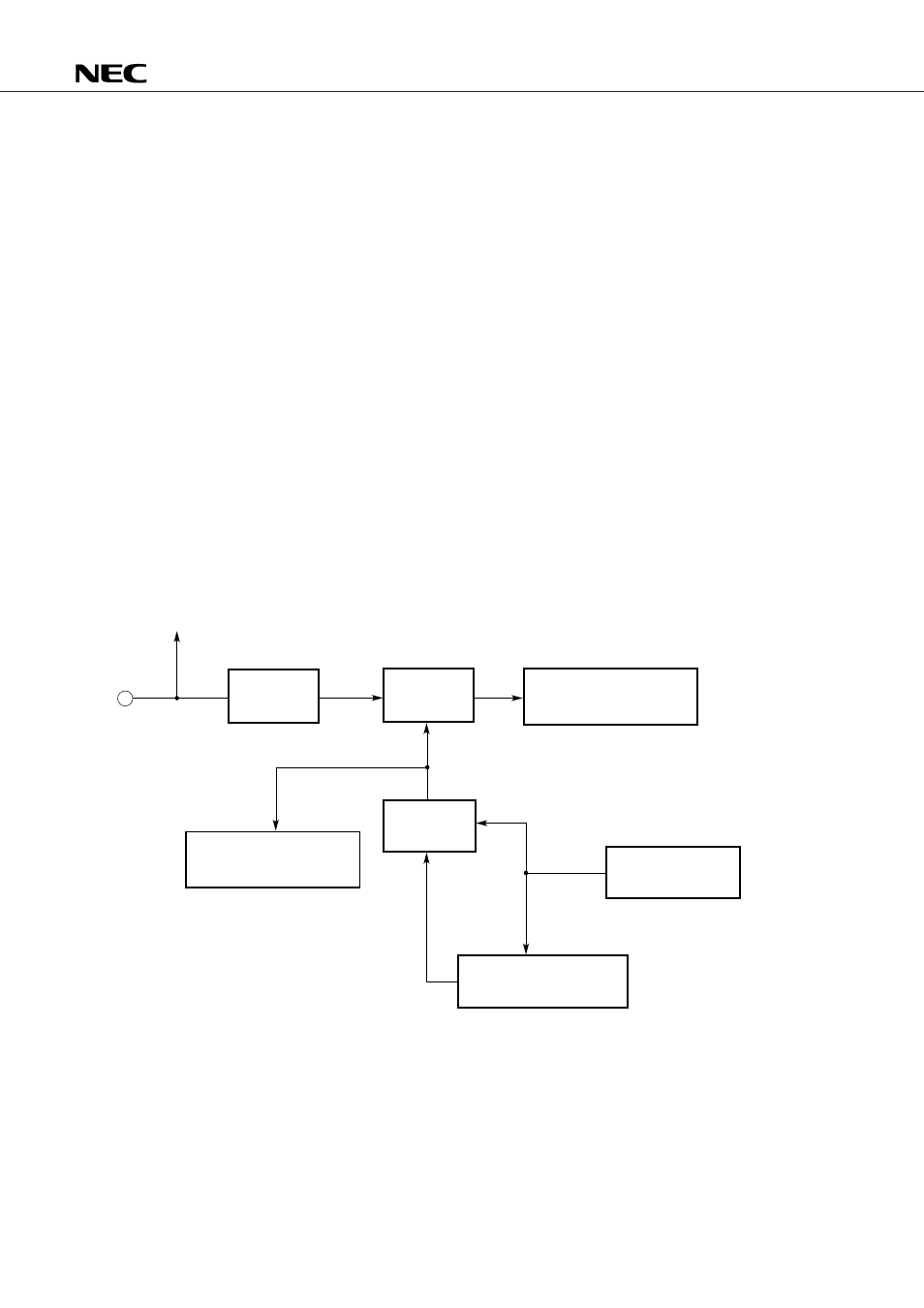

The horizontal sync signal counter consists of a 6-bit HSYNC counter (HSC), gate clock generator, gate

control register (HSCGT), gate input amplifier, and test gate open register (HSCGOSTT).

A signal supplied to the P0B

3

/HSCNT pin is amplified by the self-biased input amplifier. The output of the

amplifier passes through a gate which opens for a specific time interval specified by the gate control register.

After passing through the gate, the amplifier output is counted in the 6-bit HSYNC counter. When the gate

is closed, the HSYNC counter stops counting and sets 1 in the test gate open register. The HSYNC counter

is a read-only register. Reading the HSYNC counter finds out how many pulses are counted when the gate

is open. Dividing the number of pulses by the time during which the gate is open (1.69 ms) can obtain the

frequency of the horizontal sync signal. The P0B

3

/HSCNT pin is also used as an I/O port. It is assigned to the

P0B

3

port. When it is used as a horizontal sync signal counter, the P0B

3

must be set as an input port. When

it is used as a port, the HSCGT must be set with 0000B. When the P0B

3

is used as an input to the horizontal

sync signal counter, it is read always as 0.

Fig. 21-1 Horizontal Sync Signal Counter Block Diagram

HSCGOSTT

RF92Hb

3

(R/W)

HSCGT

RF91Hb

1

,b

0

(R/W)

Gate clock generator

To a port

Gate input

amplifier

Gate

HSYNC counter

Selector

Peripheral address 04H (R)