NEC PD17062 User Manual

Page 68

68

µ

PD17062

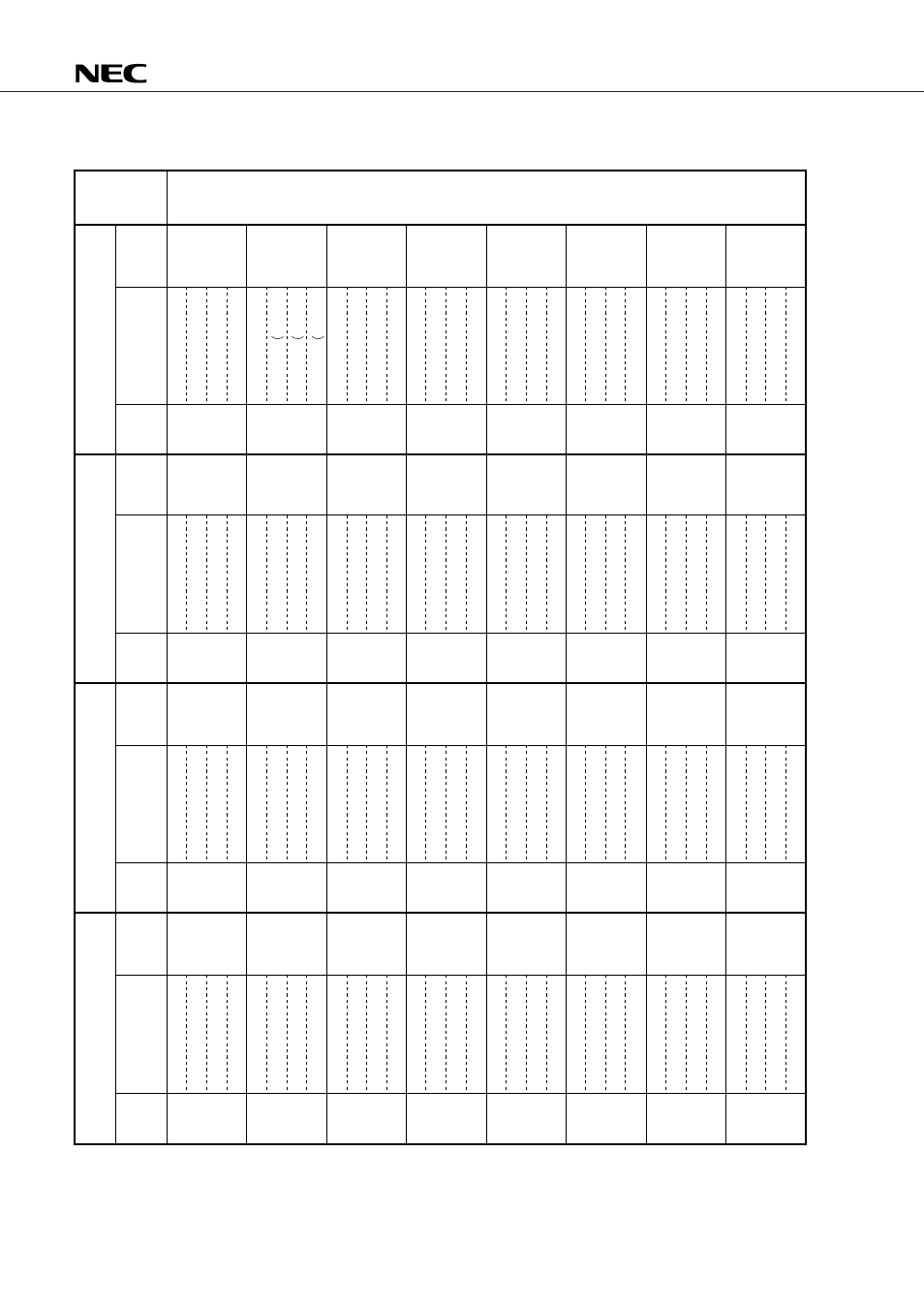

Fig. 9-1 Configuration of Control Register (1/2)

Note The number in parenthesis is the address used when the assembler (AS17K) is used.

Column Address

Row

Address

Item

0

1

2

3

4

5

6

7

0

(8)

Note

Stack pointer

(SP)

S

P

2

(

S

P

1

(

S

P

0

(

0

0

0

C

E

Read/

Write

R/W

R

1

(9)

Note

0

H

S

C

G

T

1

0

H

S

C

G

T

0

H

S

C

G

O

S

T

T

0 0

0

P

L

L

R

F

C

K

3

P

L

L

R

F

C

K

2

P

L

L

R

F

C

K

1

P

L

L

R

F

C

K

0

0

I

N

T

N

C

M

D

2

I

N

T

N

C

M

D

1

I

N

T

N

C

M

D

0

0

0

0

B

T

M

0

C

Y

Read/

Write

R/W

R

R/W

R/W

R

2

(A)

Note

A

D

C

C

H

1

A

D

C

C

H

0

A

D

C

C

M

P

0

0

0

P

L

L

U

L

0

0

0

P

1

C

G

I

O

Read/

Write

R/W

R

R/W

Read/

Write

R/W

R /W

R/W

R/W

R/W

R/W

3

(B)

Note

0

C

R

O

M

B

N

K

0

0

I

D

C

E

N

0

0

P

L

U

L

S

E

N

1

P

L

U

L

S

E

N

0

P

1

B

B

I

O

3

P

1

B

B

I

O

2

P

1

B

B

I

O

1

P

1

B

B

I

O

0

P

0

B

B

I

O

3

P

0

B

B

I

O

2

P

0

B

B

I

O

1

P

0

B

B

I

O

0

P

0

A

B

I

O

3

P

0

A

B

I

O

2

P

0

A

B

I

O

1

P

0

A

B

I

O

0

Register

CE pin level

judge register

Symbol

H

SYNC

-

counter-gate

control

register

H

SYNC

-

counter-gate

judge

register

Register

Symbol

PLL refer-

ence

clock select

register

INT

NC

mode

select

register

Basic timer 0

carry flip-flop

judge register

Register

Symbol

A/D converter

control

register

PLL-unlock-

flip-flop

judge

register

Port 1C

group I/O

select

register

IDC CROM

bank

register

Register

Symbol

IDC enable

register

PLL-unlock-

flip-flop

sensibility

select register

Port 1B bit

I/O select

register

Port 0B bit

I/O select

register

Port 0A bit

I/O select

register

IDCDMA

enable

register

0

I

D

C

D

M

A

E

N

0

0

0

R/W

A

D

C

C

H

2

0

0

0