NEC PD17062 User Manual

Page 182

182

µ

PD17062

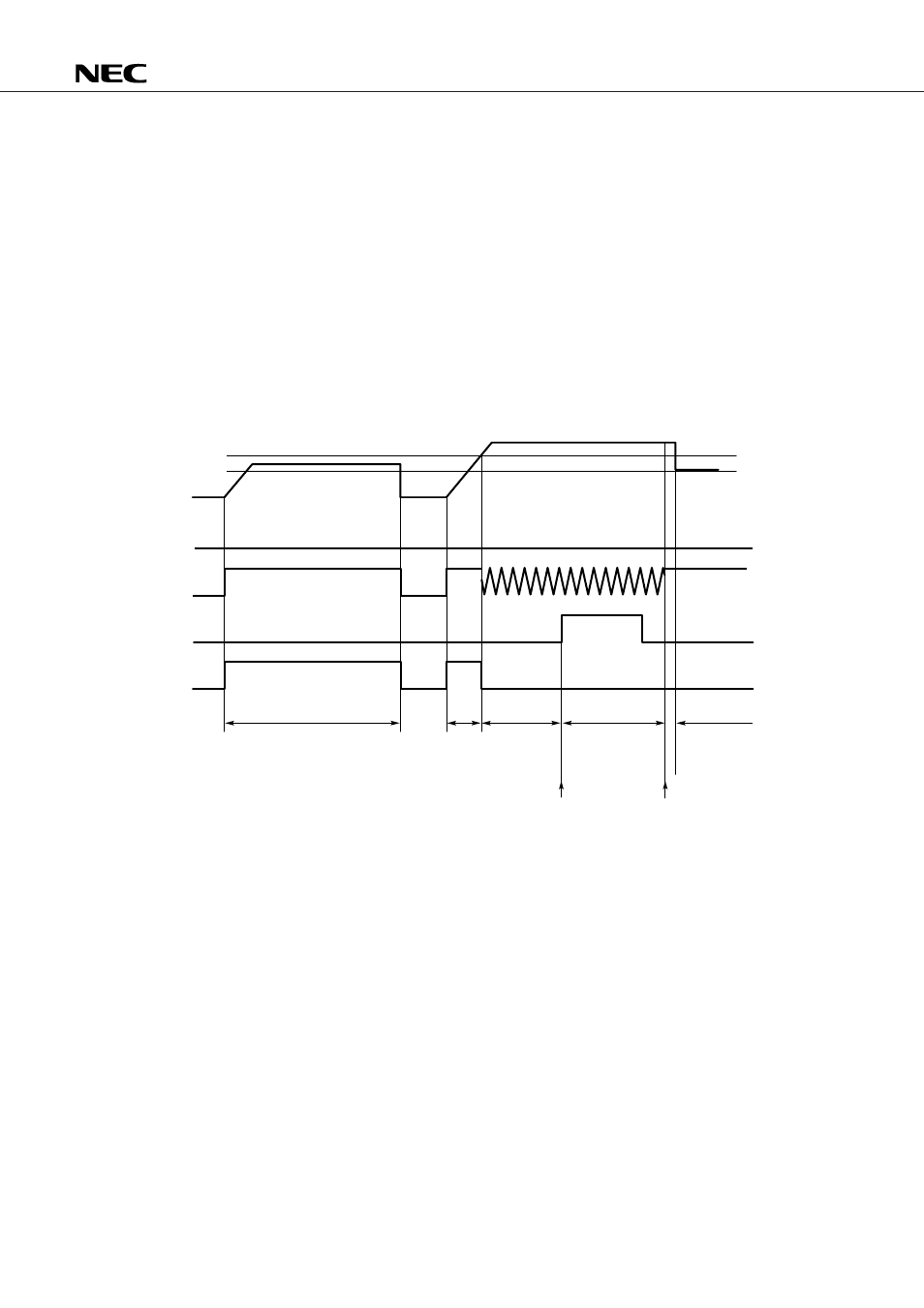

14.5.4 Cautions When Supply Voltage Raised

When supply voltage is raised, careful attention must be given to points (1) and (2) below.

(1) When V

DD

raised from power-on clear voltage

When V

DD

is raised, it must be raised to 3.5 V or greater, once.

This is shown in Fig. 14-7.

As shown in Fig. 14-7, when a voltage under 3.5 V is applied when V

DD

is turned on in a program that uses

clock-stop to back up V

DD

at 2.2 V, for example, the power-on clear signal continues to be output and the

program does not run.

Since the device output port outputs an undefined value, the supply current increases, according to the

situation, reducing the back-up time with a battery considerably.

Fig. 14-7 Caution When V

DD

Raised

5 V

0 V

Operation stopped

X

OUT

V

DD

CE

Power-on

clear signal

Timer carry FF

set pulse

3.5 V

2.2 V

Opera-

tion

stopped

Halt state

50 ms

Normal operation

Back-up

Since the values of the output

ports, etc. are undefined during

this period, the current drain

may increase.

During this period,

initialization is per-

formed, then the

clock is stopped.

Power-on reset

Program start

STOP 0000B

Power-on

clear voltage