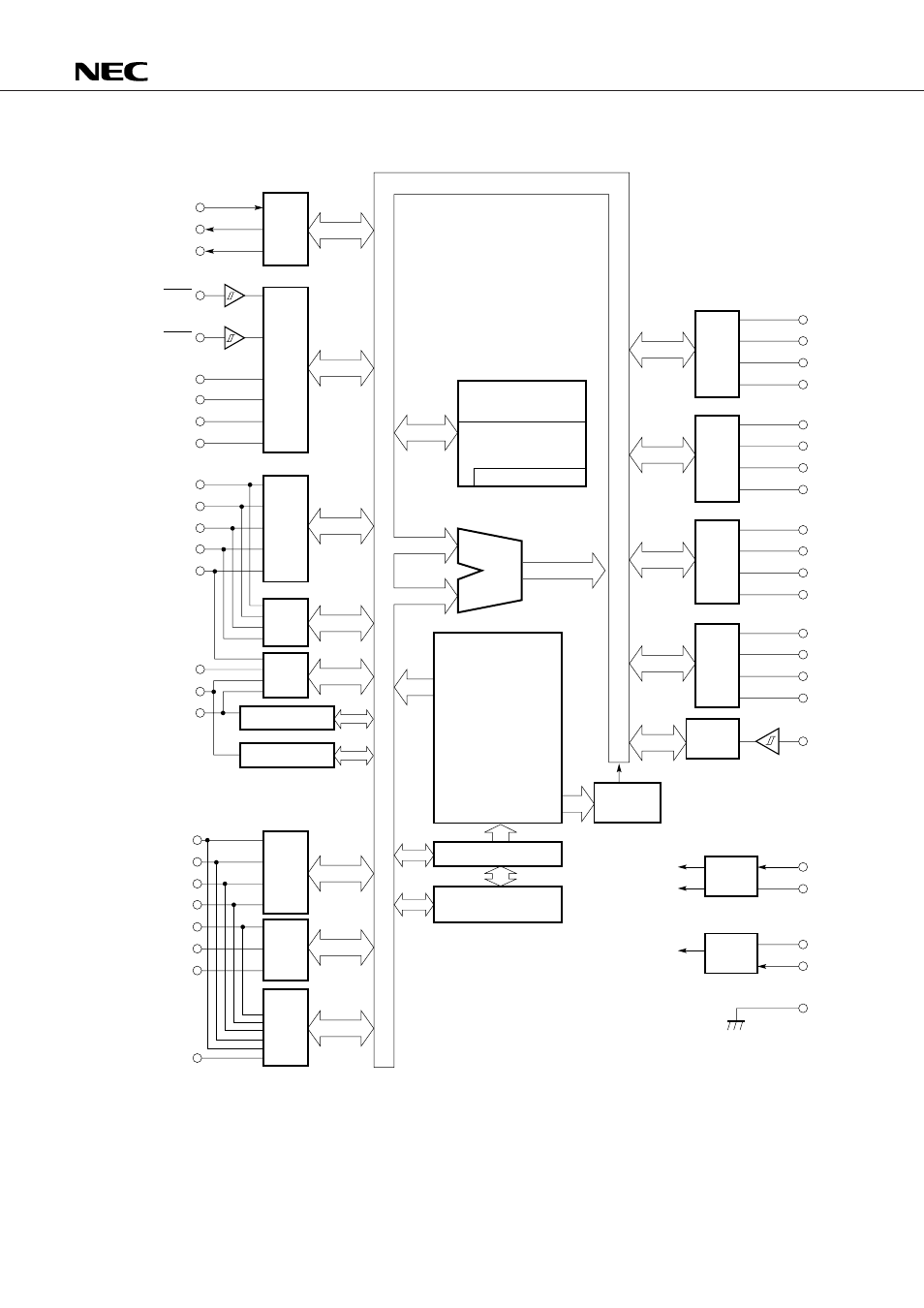

Block diagram – NEC PD17062 User Manual

Page 5

5

µ

PD17062

BLOCK DIAGRAM

VCO

PSC

EO

H

SYNC

V

SYNC

RED

GREEN

BLUE

BLANK

P0A

0

/SDA

P0A

1

/SCL

P0A

2

/SCK

P0A

3

/SO

P0B

0

/SI

P0B

1

P0B

2

/TMIN

P0B

3

/HSCNT

P0D

0

/ADC

2

P0D

1

/ADC

3

P0D

2

/ADC

4

P0D

3

/ADC

5

P1C

3

/ADC

1

P1C

2

P1C

1

ADC

0

PWM

0

PWM

1

PWM

2

PWM

3

P1A

0

P1A

1

P1A

2

P1A

3

P1B

0

P1B

1

P1B

2

P1B

3

P0C

0

P0C

1

P0C

2

P0C

3

INT

NC

X

IN

X

OUT

V

DD

CE

GND

CPU

Peripheral

Instruction

Decoder

Interrupt

Controller

P0C

P1B

P1A

PWM

PLL

IDC

Serial

I/O

P0A

P0B

Hsync Counter

Timer Controller

RF

RAM

336

×

4 bits

(Including VRAM)

SYSREG

ALU

ROM

3968

×

16 bits

(Including CROM)

Program Counter

Stack 6

×

12 bits

OSC

Reset

P0D

P1C

A/D