3 address stack registers (asrs), 4 interrupt stack registers – NEC PD17062 User Manual

Page 27

27

µ

PD17062

4.3 ADDRESS STACK REGISTERS (ASRs)

There are six address stack registers, each consisting of 13 bits. After a subroutine call instruction has been

executed or an interrupt request accepted, the contents of the address stack register will contain a value that

is equal to the contents of the program counter, plus one, or the return address. The contents of an address

stack register are loaded into the program counter by executing a return instruction, after which control returns

to the original program flow.

The address stack registers are used for both subroutine calls and interrupts. If two levels of the address

stack registers are used for interrupts, the remaining four levels can be used for subroutine calls.

If a MOVT instruction is executed, an address stack register is used temporarily.

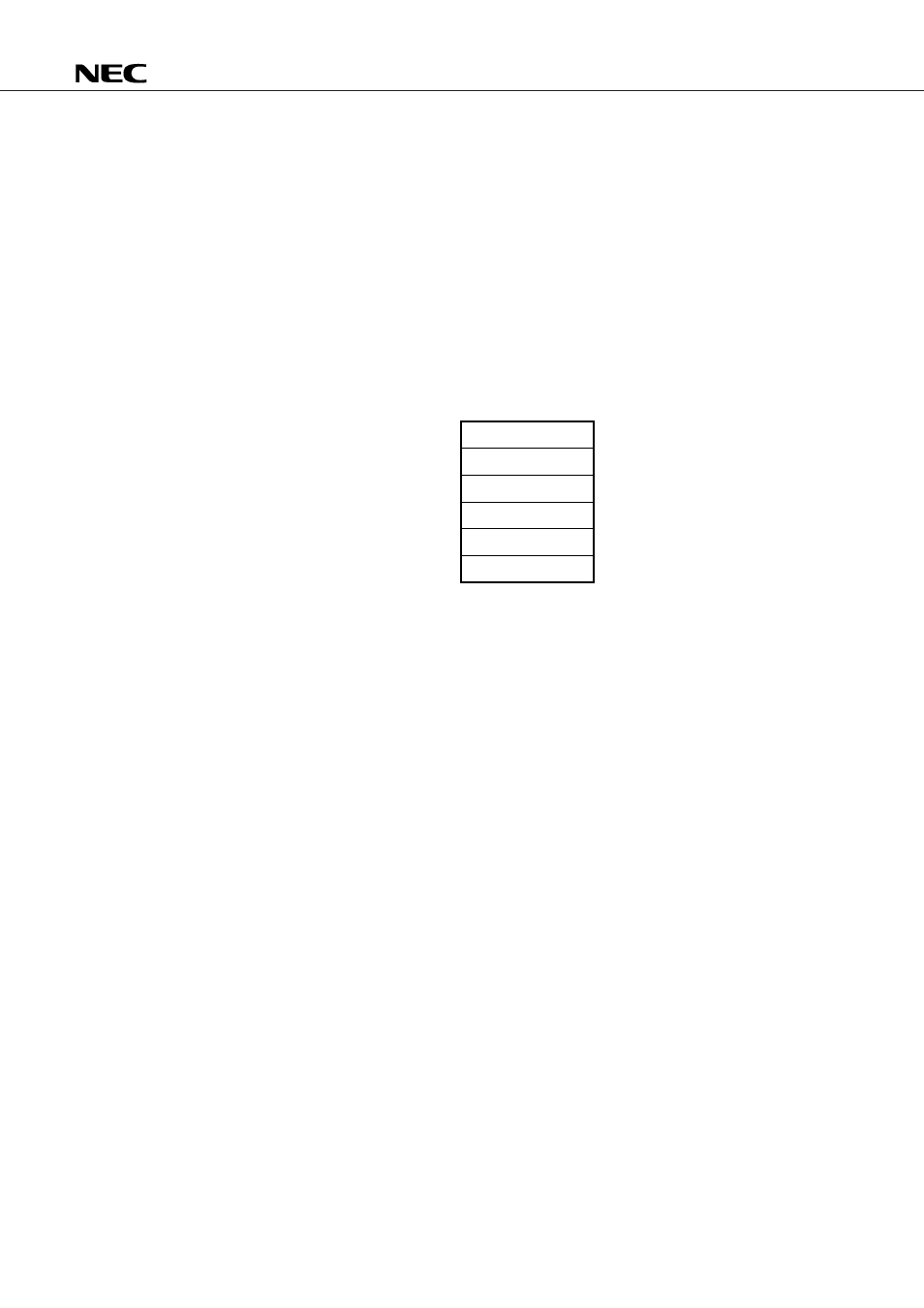

Fig. 4-2 Structure of Address Stack Registers

4.4 INTERRUPT STACK REGISTERS

There are two interrupt stack registers, each consisting of three bits, as shown in Fig. 4-3.

If an interrupt is accepted, the value of the two bits of the bank register (BANK) and the value of the one

bit of the index-enable flag (IXE) in the system register (SYSREG), described later, are saved to an interrupt

stack register. Once an interrupt return instruction (RETI) has been executed, the contents of the interrupt

stack register are returned to the bank register and the index-enable flag of the system register.

Unlike the address stack registers, the interrupt stack registers contain no addresses specified by the stack

pointer. As shown in Fig. 4-4, data is saved to an interrupt stack pointer each time an interrupt is accepted,

the saved data being returned whenever an interrupt return instruction is executed. If accepted interrupts

consist of more than two levels, the first level of data is pushed out. Thus, it must be saved by the program.

If a power-on reset is performed, the contents of the interrupt stack registers become undefined. Even if

a CE reset is performed or a clock stop instruction is executed, however, the contents of the interrupt stack

registers remain as is.

ASR

0

ASR

1

ASR

2

ASR

3

ASR

4

ASR

5

0H

1H

2H

3H

4H

5H

Stack pointer value