NEC PD17062 User Manual

Page 73

73

µ

PD17062

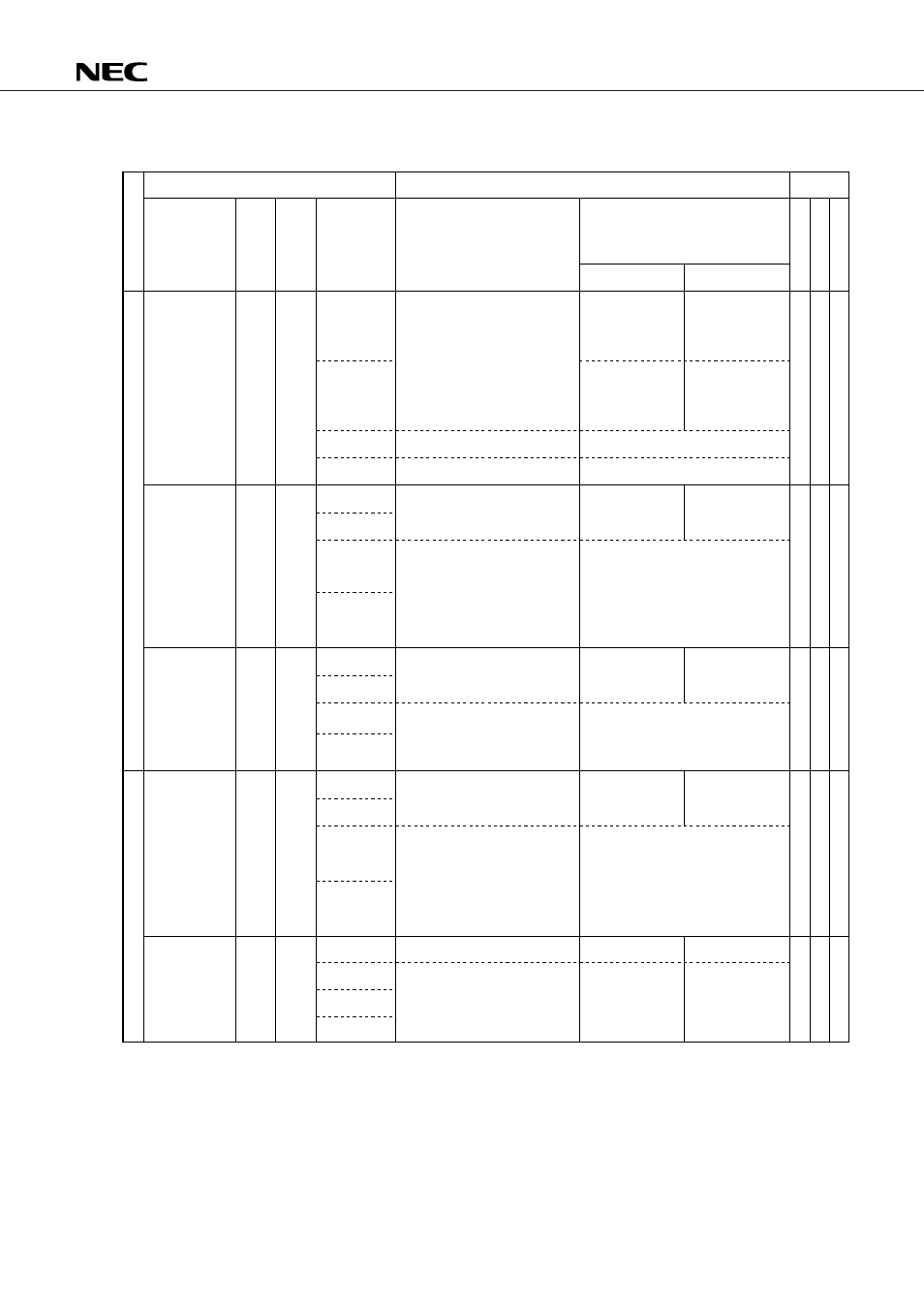

Table 9-1 Peripheral Hardware Control Functions of Control Registers (4/5)

Remark *: Retains the previous state. **: Indefinite

Peripheral hardware

Control register

Peripheral hardware control function

At reset

Register

Ad-

dress

Read/

write

b3

b2

b1

b0

Symbol

Function outline

Set value

0

1

P

o

w

e

r

O

n

S

T

O

P

C

E

Serial interface

Horizontal synchronizing signal counter

Serial I/O0

status judge

register

Serial I/O0

interrupt

mode

register

Serial I/O0

clock select

register

H

SYNC

counter

gate control

register

H

SYNC

counter

gate judge

register

28H

R

38H

R/W

39H

R/W

11H

R/W

12H

R

SIO0SF8

SIO0SF9

SBSTT

SBBSY

0

0

SIO0IMD1

SIO0IMD0

0

0

SIO0CK1

SIO0CK0

0

0

HSCGT1

HSCGT0

HSCGOSTT

0

0

0

Detects the contents of clock

counter

Detects the number of clocks

(I

2

C bus method)

Detects the start condition

(I

2

C bus method)

Fixed at 0

Sets the interrupt condition

of serial interface 0

Fixed at 0

Fixed at 0

Sets the internal clock of

serial interface 0

Controls the H

SYNC

counter gate

Detects open/close of the H

SYNC

counter

Fixed at 0

0

0

0

Resets when

the contents of

the clock counter

become 0 or 1

Resets when

the contents of

the clock counter

become 0 or 1

Resets when

the contents of

the clock counter

become 8

Resets when

the contents of

the clock counter

become 9

Sets up the start condition - 9th clock

Sets up the start condition -

stop condition

0

0

1

1

0

1

1

0

7th

clock

8th

clock

7th clock

after occur-

rence of start

condition

Stop

con-

dition

0

0

1

1

0

1

1

0

Gate

close

Gate

open

1.69 ms

gate

open

Not to

be set

Gate open

Gate close

0

0

1

1

0

1

1

0

100

kHz

200

kHz

500

kHz

1

MHz

** *

*

** *

*

0

0

0

0

–

–