1 address register (ar), 2 window register (wr) – NEC PD17062 User Manual

Page 55

55

µ

PD17062

b

3

0

b

2

0

b

1

0

b

0

0

b

3

0

b

2

0

b

1

0

b

0

0

b

3

b

2

b

1

b

0

b

3

b

2

b

1

b

0

AR

15

(MSB)

AR

0

(LSB)

AR0

(77H)

AR1

(76H)

AR2

(75H)

AR3

(74H)

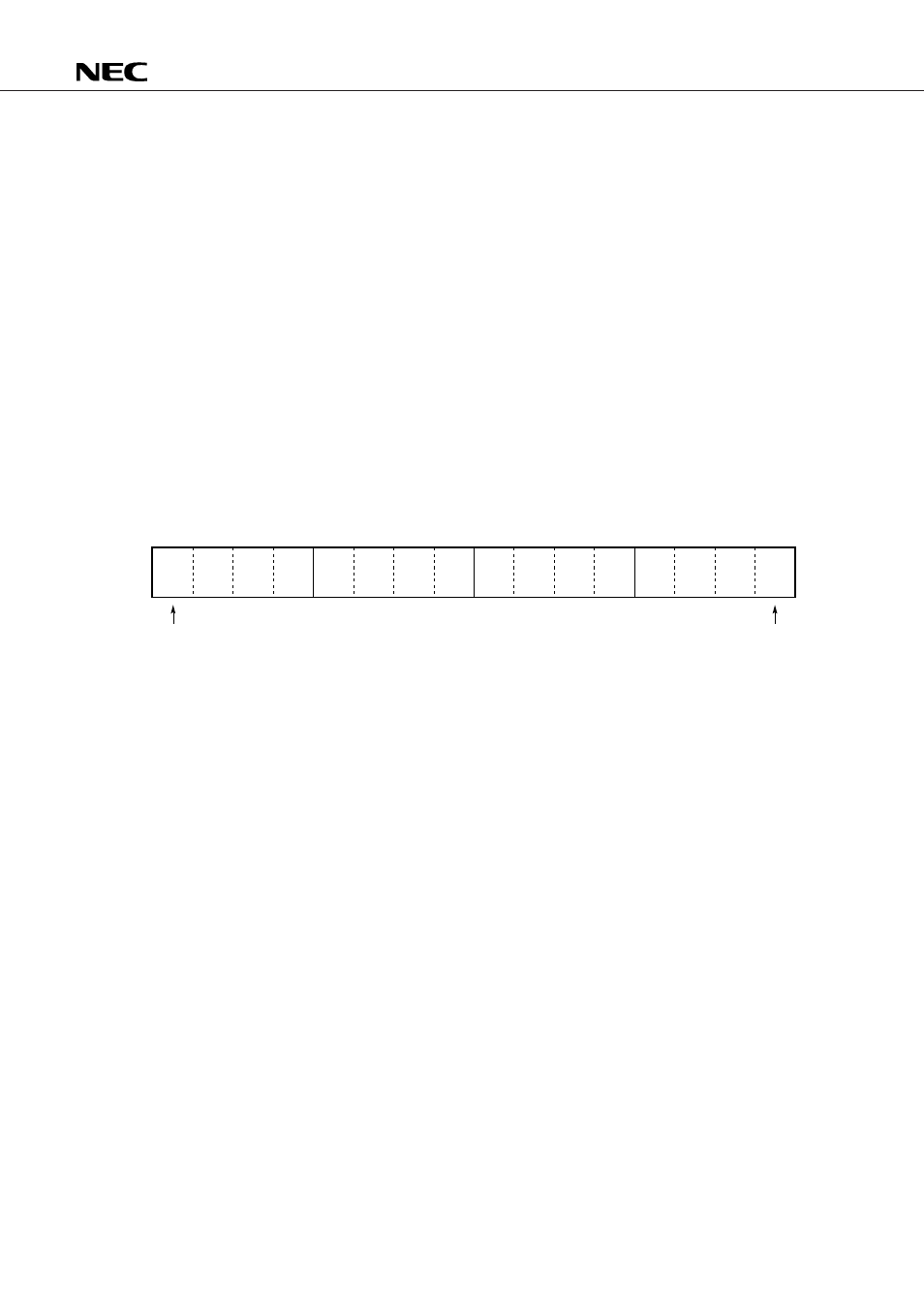

8.1 ADDRESS REGISTER (AR)

The address register specifies a program memory address. It is located at addresses 74H-77H. The

instructions used to manipulate the address register are indirect branch instructions (BR @AR, CALL @AR),

the table reference instruction (MOVT), and stack manipulation instructions (PUSH, POP).

An indirect branch is a branch to the program memory address specified by the contents of the address

register. Indirect branch instructions include BR @AR and CALL @AR.

Table reference is the transfer of the contents of the program memory address specified by the address

register to the DBF of data memory (BANK0 0DH-0FH). This is done by executing a MOVT instruction.

Stacks are manipulated using the PUSH and POP instructions. The PUSH instruction stores the contents

of the address register in the stack specified by the current stack pointer, and decrements the contents of the

stack pointer by 1. The POP instruction increments the contents of the stack pointer by 1, and loads the contents

of the stack specified by the current stack pointer into the address register.

AR3 and AR2 of

µ

PD17062 are fixed at 0. Hence, the program address that can be specified by the address

register is the 256 steps of 0000H-00FFH.

Fig. 8-2 Configuration of Address Register

8.2 WINDOW REGISTER (WR)

The window register is a 4-bit register, mapped to address 78H of the system register. It is used for data

transfer together with the register file (RF), described later in this manual. All data in each register of the

register file is manipulated via the window register.

Data transfer between the window register and the register file is achieved by execution of the exclusive

PEEK WR, rf and POKE rf, WR instructions.