6 power failure detection – NEC PD17062 User Manual

Page 184

184

µ

PD17062

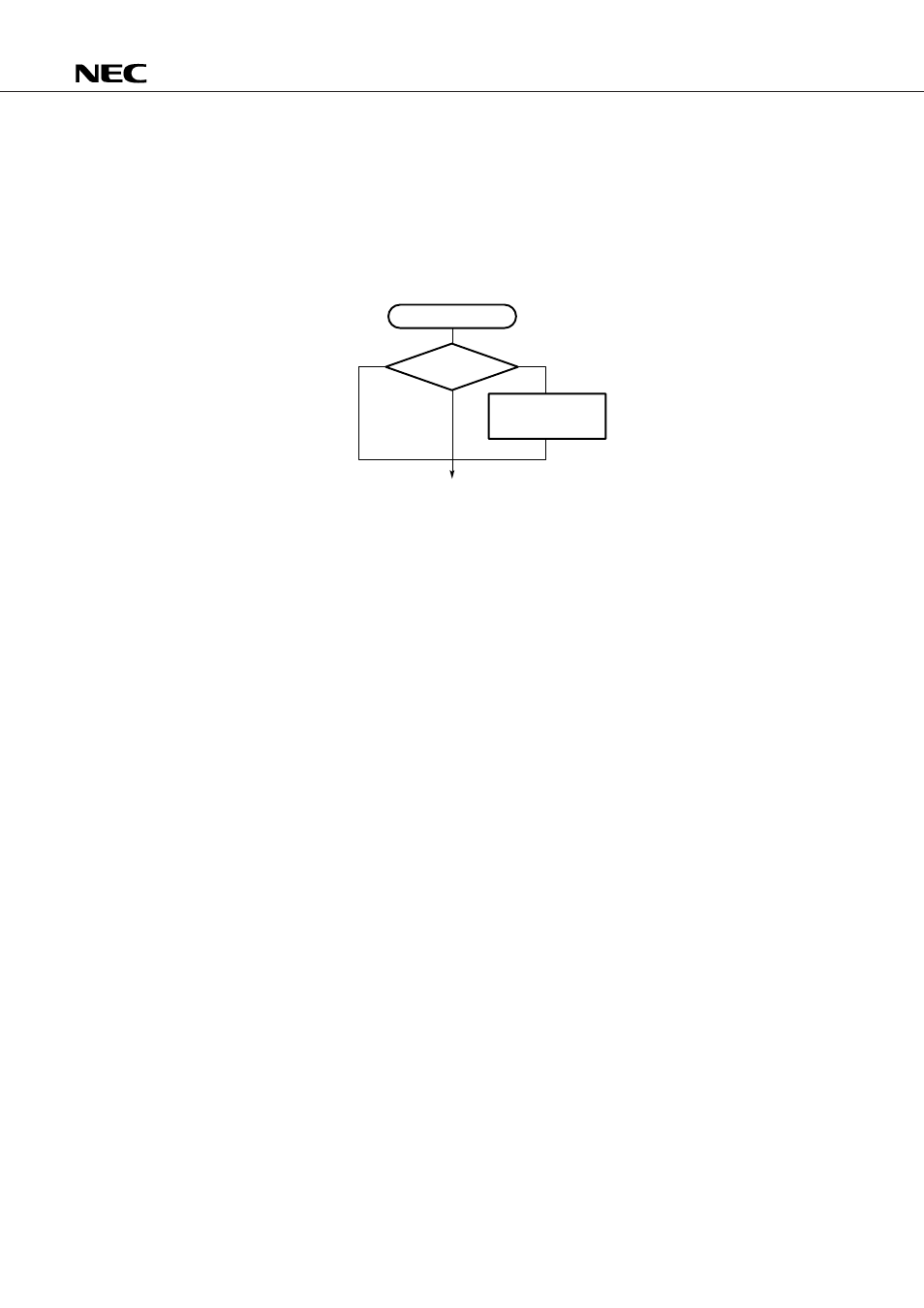

14.6 POWER FAILURE DETECTION

Power failure detection is used to judge whether the device is reset by turning on V

DD

or by the CE pin, as

shown in Fig. 14-9.

Since the contents of the data memory, output ports, etc. become “undefined” when V

DD

is turned on, they

are initialized by power failure detection.

Fig. 14-9 Power Failure Detection Flowchart

14.6.1 Power Failure Detection Circuit

As shown in Fig. 14-1, the power failure detection circuit consists of a voltage detection circuit and timer

carry disable FF that is reset by the output (power-on clear signal) of the voltage detection circuit, and timer

carry FF.

The timer carry disable FF is set to 1 by the power-on clear signal and is reset to 0 when a BTM0CY flag

(address 17H, bit b

0

) read instruction is executed.

When the timer carry disable FF is set to 1, the BTM0CY flag is not set to 1.

That is, when the power-on clear signal is output (at power-on reset), the program starts in the state in which

the BTM0CY flag is reset and the setting disabled state is set until a BTM0CY read instruction is executed

thereafter.

Once a BTM0CY read instruction is executed, the BTM0CY flag is set at each rising edge of the timer carry

FF set pulse thereafter. When reset is applied to the device, the contents of the BTM0CY flag are monitored.

If the BTM0CY flag has been reset to 0, power-on reset (power failure) is judged and if the BTM0CY flag has

been set to 1, CE reset (no power failure) is judged.

Since the voltage that can detect a power failure is the same as the voltage applied by power-on reset, V

DD

becomes 3.5 V at clock oscillation and 2.2 V at clock-stop.

Fig. 14-10 shows the BTM0CY flag state transition.

Fig. 14-11 shows timing chart and BTM0CY flag operation specified in Fig. 14-10.

Program start

Power failure

No power failure

Data memory,

output port, etc.

initialization

Power

failure detect-

ion