NEC PD17062 User Manual

Page 95

95

µ

PD17062

10.4.2 Precautions When Transferring Data With Peripheral Registers

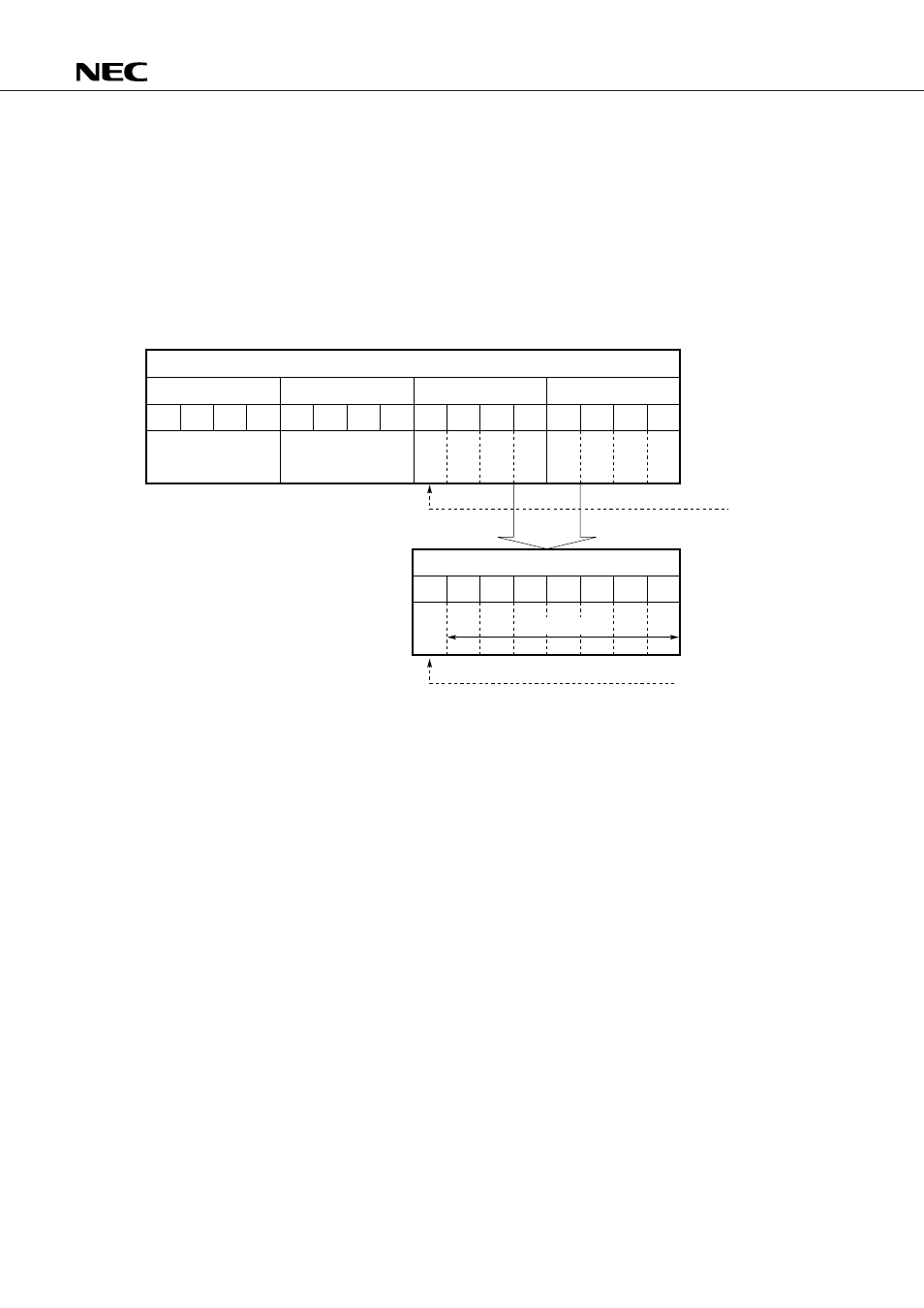

Data is transferred between the data buffer and peripheral registers in 8-bit or 16-bit units.

A PUT or GET instruction is executed for one instruction cycle (2

µ

s) even if the data is 16 bits long.

When 8-bit data transfer is performed but the peripheral register execution data is seven bits, for example,

long one extra bit is added.

At data write, the status of this extra data is “Don’t care” as shown in Example 1. At data read, the status

of this extra data is “Unpredictable” as shown in Example 2.

Example 1. PUT instruction (When the valid peripheral register bits are seven bits from bit

0

to bit

6

.)

When 8-bit data is written to a peripheral register, the status of the eight high-order bits of the data buffer

(contents of DBF3 and DBF2) is “Don’t care”.

Of the 8-bit data in the data buffer, the status of each bit that does not correspond to a valid bit in the

peripheral register is “Don’t care”.

DBF3

DBF2

DBF1

DBF0

b

15

b

14

b

13

b

12

b

11

b

10

b

9

b

8

b

7

b

6

b

5

b

4

b

3

b

2

b

1

b

0

Peripheral register

b

7

b

6

b

5

b

4

b

3

b

2

b

1

b

0

PUT

Data buffer

8

0 or unpredictable

Don't care

Don't care

Don't care

(Can be any value)

Valid bits