6 stratixgx interconnect, 1 pld registers, 1 data registers – Artesyn ATCA-9305 User's Manual (May 2014) User Manual

Page 83: Table 3-8, Data 31:24 (0x0), Cavium processor complex

Cavium Processor Complex

ATCA-9305 User’s Manual (10009109-07)

83

3.6

StratixGX Interconnect

The Altera StratixGX FPGA provides the high-speed SPI-4.2 interconnect. Each complex has

dual SPI-to-XAUI bridges connected to the XAUI Ethernet switch ports.

3.6.1

PLD Registers

The FPGA bridge is located at address 0x1D030000. Use the following registers to access the

XAUI to SPI bridge configuration registers.

3.6.1.1

Data Registers

PLD registers information can be requested via sales/marketing office.

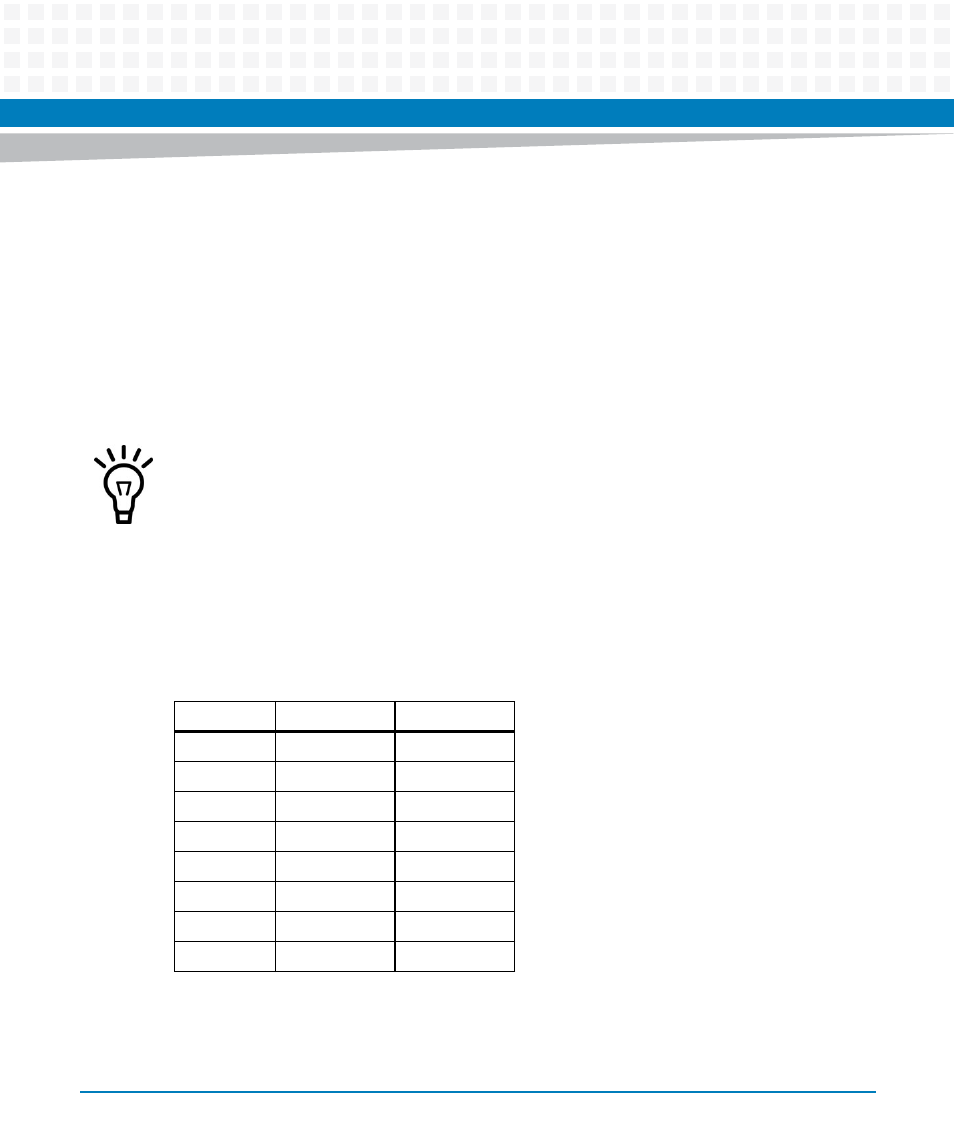

Table 3-8 Data 31:24 (0x0)

Bits

R/W

Function

7

R/W

Data 31

6

R/W

Data 30

5

R/W

Data 29

4

R/W

Data 28

3

R/W

Data 27

2

R/W

Data 26

1

R/W

Data 25

0

R/W

Data 24

See also other documents in the category Artesyn Equipment:

- ARTM-9405 16x10GbE Installation and Use Guide (May 2014) (64 pages)

- ATCA 7370 / ATCA 7370-S Installation and Use (January 2015) (256 pages)

- ATCA 7370 / ATCA 7370-S Installation and Use (September 2014) (254 pages)

- ARTM-831X Installation and Use (June 2014) (346 pages)

- ATCA-7350 - Integrating with Workbench User Guide (September 2014) (34 pages)

- ATCA-7350 Installation and Use (September 2014) (208 pages)

- ATCA-7365-CE Installation and Use (Jan 2015) (300 pages)

- ATCA-7365-CE Installation and Use (May 2014) (294 pages)

- ATCA-7365-CE Installation and Use (May 2014) (306 pages)

- ATCA-7368 Installation and Use (June 2014) (222 pages)

- ATCA-7475 Installation and Use (October 2014) (284 pages)

- ATCA-7480 Installation and Use (April 2015) (330 pages)

- ATCA-8330 Installation and Use (April 2015) (236 pages)

- ATCA-8320 Installation and Use (May 2014) (456 pages)

- ATCA-9405 Installation and Use (October 2014) (168 pages)

- ATCA-F120 Installation and Use (August 2014) (122 pages)

- ATCA-F140 Installation and Use (September 2014) (138 pages)

- ATCA-MF106 Installation and Use (September 2014) (86 pages)

- Centellis-4440/AXP1440 Installation and Use (September 2014) (208 pages)

- Centellis 4410 (AXP-1410) Installation and Use (July 2014) (202 pages)

- Centellis 2100 Release 3.0 Installation and Use (March 2015) (192 pages)

- Centellis 2100 Release 3.0 Installation and Use (March 2015) (176 pages)

- Centellis 2000 User Card-10GE Installation and Use (May 2014) (54 pages)

- Centellis 2000 User Card-10GE with Telco Alarm Installation and Use (May 2014) (60 pages)

- COMX-CAR-210 Installation and Use (August 2014) (76 pages)

- COMX-P1022 Installation and Use (July 2014) (84 pages)

- COMX-P2020 Installation and Use (February 2015) (100 pages)

- COMX-CORE Series Installation and Use (August 2014) (128 pages)

- COMX-P2020 Installation and Use (July 2014) (100 pages)

- COMX-P4080-2G-ENP2 Installation and Use (August 2014) (70 pages)

- COMX-P4080 Installation and Use (August 2014) (126 pages)

- COMX-P40x0 ENP2 Installation and Use (August 2014) (130 pages)

- COMX-P40x0 ENP2 Installation and Use (January 2015) (140 pages)

- iVPX7225 RTM Installation and Use (April 2015) (56 pages)

- MITX-430/MITX-440-DVI-2E Installation and Use (August 2014) (118 pages)

- CPCI-6200 Installation and Use (May 2015) (234 pages)

- SCP-MITX-CORE-820-SM Installation and Use (August 2014) (132 pages)

- iVPX7225 Installation and Use (April 2015) (168 pages)

- MVME2502 Installation and Use (August 2014) (150 pages)

- MVME2502 Installation and Use (December 2014) (166 pages)

- MVME2500 VxWorks 6.8 AMP User Guide (August 2014) (40 pages)

- MVME2500 VxWorks 6.8 User Guide (April 2014) (44 pages)

- MVME3100 Single Board Computer Installation and Use (June 2014) (156 pages)

- MVME4100 Single Board Computer Installation and Use (June 2014) (136 pages)