1 cavium memory map, Table 3-1, Cn5860 features – Artesyn ATCA-9305 User's Manual (May 2014) User Manual

Page 70: Table 3-2, Cavium address summary, Cavium processor complex

Cavium Processor Complex

ATCA-9305 User’s Manual (10009109-07)

70

The main features of the CN5860 include:

The CN5860 and switch route packets using SPI-4.2 and control information flow using PCI.

The CN5860 has two SPI-4.2 interfaces with each one supporting up to 16 ports. Two high-

speed SPI-4.2 Altera (Stratix™ GX) FPGAs function as the SPI-to-XAUI bridge for each processor

to switch complex. The PCI interface supports up to four ports, consequently a total of 36 ports

can be supported internally by each CN5860.

3.1.1

Cavium Memory Map

Although the Cavium processors are 64-bit, the ATCA-9305 uses a 49-bit implementation.

Refer to the Cavium Networks OCTEON Plus CN58xx Hardware Reference Manual for more

detailed information on the memory map.

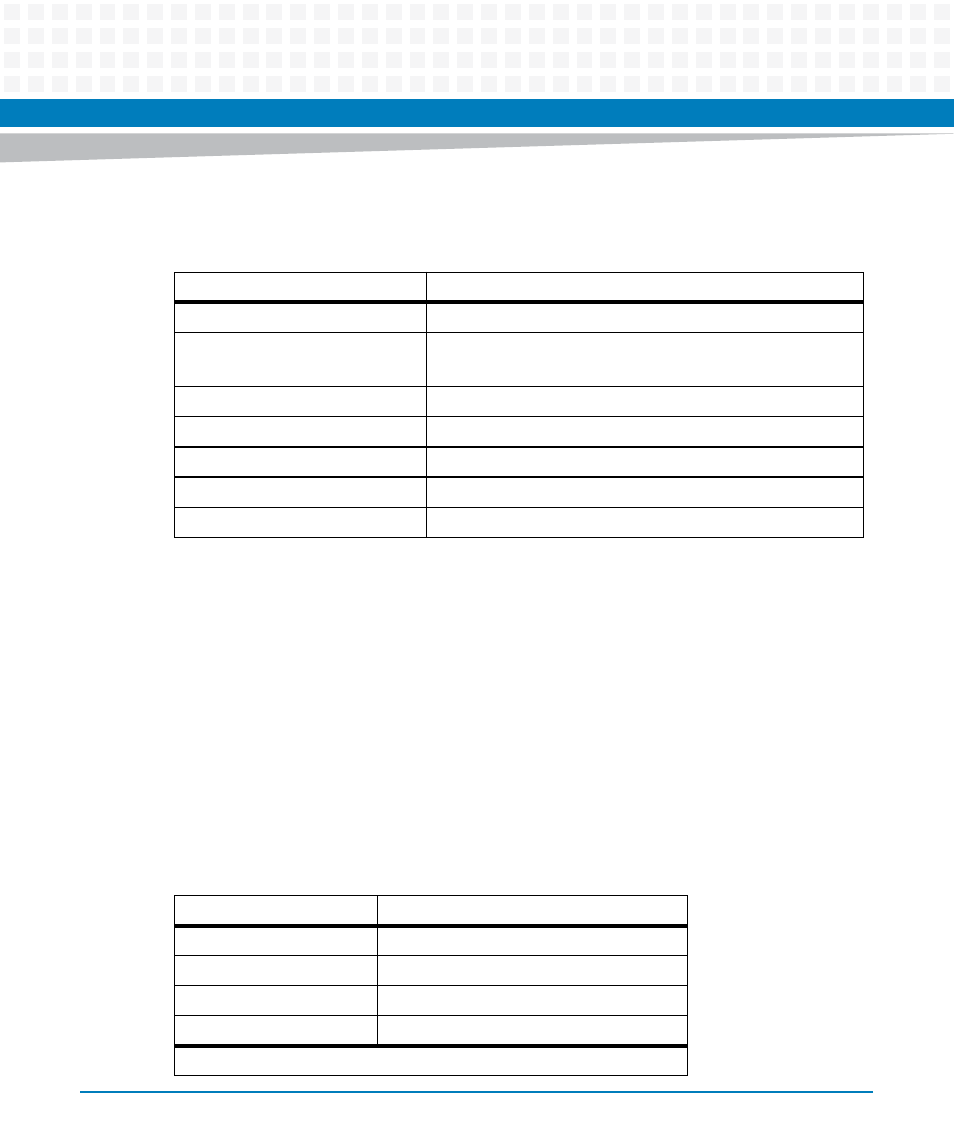

Table 3-1 CN5860 Features

Feature

Description

Processor Core

Up to 16 cnMIPS™ cores

Core Speed

Network Services Processor (NSP)

up to 800 MHz, processing up to 30 million packets per second

System Packet Interface

Two SPI-4.2 ports

L2 Cache

2 MB, eight-way set associative

DRAM

144-bit DDR2 DRAM interface

RLDRAM

18-bit RLDRAM, low-latency memory direct access

PCI

64-bit, PCI 2.3 compatible

Table 3-2 Cavium Address Summary

Hex Physical Address

Register Description

1,2000,0000,0000

reserved

1,1F00,0000,0000

Cavium Hardware registers

1,1E00,0000,0000

PCI Memory Space (6)

1,1D00,0000,0000

PCI Memory Space (5)

This depends on how much memory is installed.