15 reset command sticky #2, 16 boot device redirection, Table 5-16 – Artesyn ATCA-9305 User's Manual (May 2014) User Manual

Page 116: Reset command sticky #2 (0x3c), Table 5-17, Boot device redirection (0x50), Management processor cpld

Management Processor CPLD

ATCA-9305 User’s Manual (10009109-07)

116

5.1.15 Reset Command Sticky #2

The read/write Reset Command Sticky #2 register forces one of several types of the PHY reset

command, as shown below. A reset sequence is first initiated by writing a one to one or more

bits, then the PLD performs that particular reset. The bit will persist until cleared.

5.1.16 Boot Device Redirection

The read/write Boot Device Redirection register (BDRR) allows the user to determine which of

three boot devices the MPC8548 CPU is using as the boot device. Several bits also indicate

which device was set as the initial boot device. The Boot Redirected bit is set to a 1 when the

current boot device does not match the initial default boot device. This indicates to the user

that the image in the default device was bad, the MPC8548 watch dog timer expired, and the

next device was tried. The boot device redirection order is determined by IPMC. Reference the

“

”.

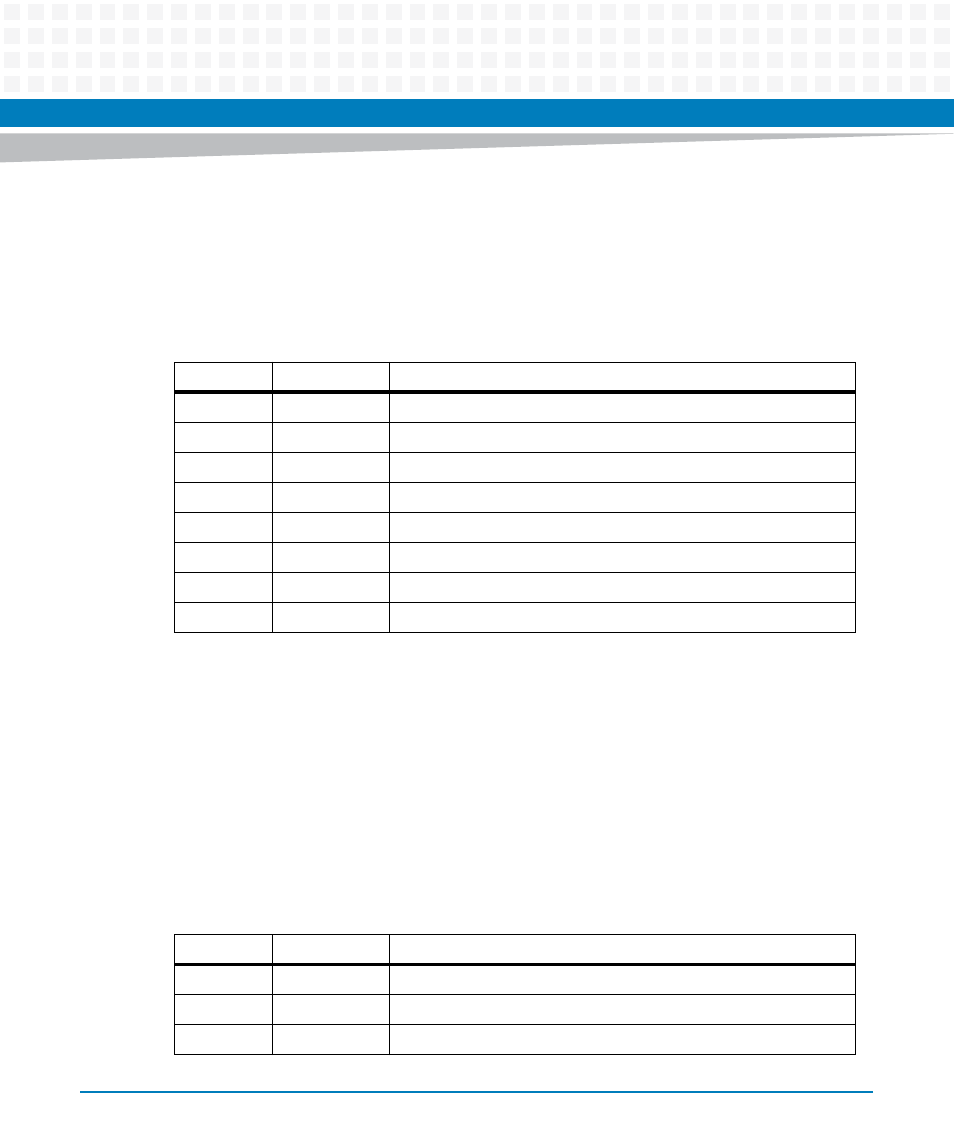

Table 5-16 Reset Command Sticky #2 (0x3C)

Bits

Function

Description

7

TSEC1R

TSEC1 Ethernet to front panel PHY Reset

6

TSEC2R

TSEC2 Ethernet to switch PHY Reset

5

FPIR

FPI Ethernet from switch to front panel PHY Reset

4

BCR

Ethernet dual PHY to backplane Base Channel Reset

3

MIP1

SPI to XAUI bridge #1 on Cavium 1

2

MIP2

SPI to XAUI bridge #2 on Cavium 1

1

MIP3

SPI to XAUI bridge #3 on Cavium 2

0

MIP4

SPI to XAUI bridge #4 on Cavium 2

Table 5-17 Boot Device Redirection (0x50)

Bits

Function

Description

7

SELFRS

Self Refresh Started

6

BOOTSEL1

IPMC successful boot indication (BOARD_BOOTED)

5

reserved