3 pld version, 4 pll reset configuration, 3 pld version 5.1.4 pll reset configuration – Artesyn ATCA-9305 User's Manual (May 2014) User Manual

Page 108: Table 5-4, Pld version (0x08), Table 5-5, Pll reset configuration (0x0c), Management processor cpld

Management Processor CPLD

ATCA-9305 User’s Manual (10009109-07)

108

5.1.3

PLD Version

This read-only register tracks PLD revisions.

5.1.4

PLL Reset Configuration

Write to this register to reconfigure the SYSCLK to CCB clock ratio and the CCB to CORE clock

ratio using valid values from the MPC8548E PowerQUICC

™

III Integrated Processor Family

Reference Manual. The changes take affect when the processor is reset (for example, the

software hard reset command or watchdog timer expires). Default values are restored when

the board is power-cycled, front panel reset is pressed, or receives a PCI reset that was not the

result of the MPC8548 software initiating a PCI RSTOUT command.

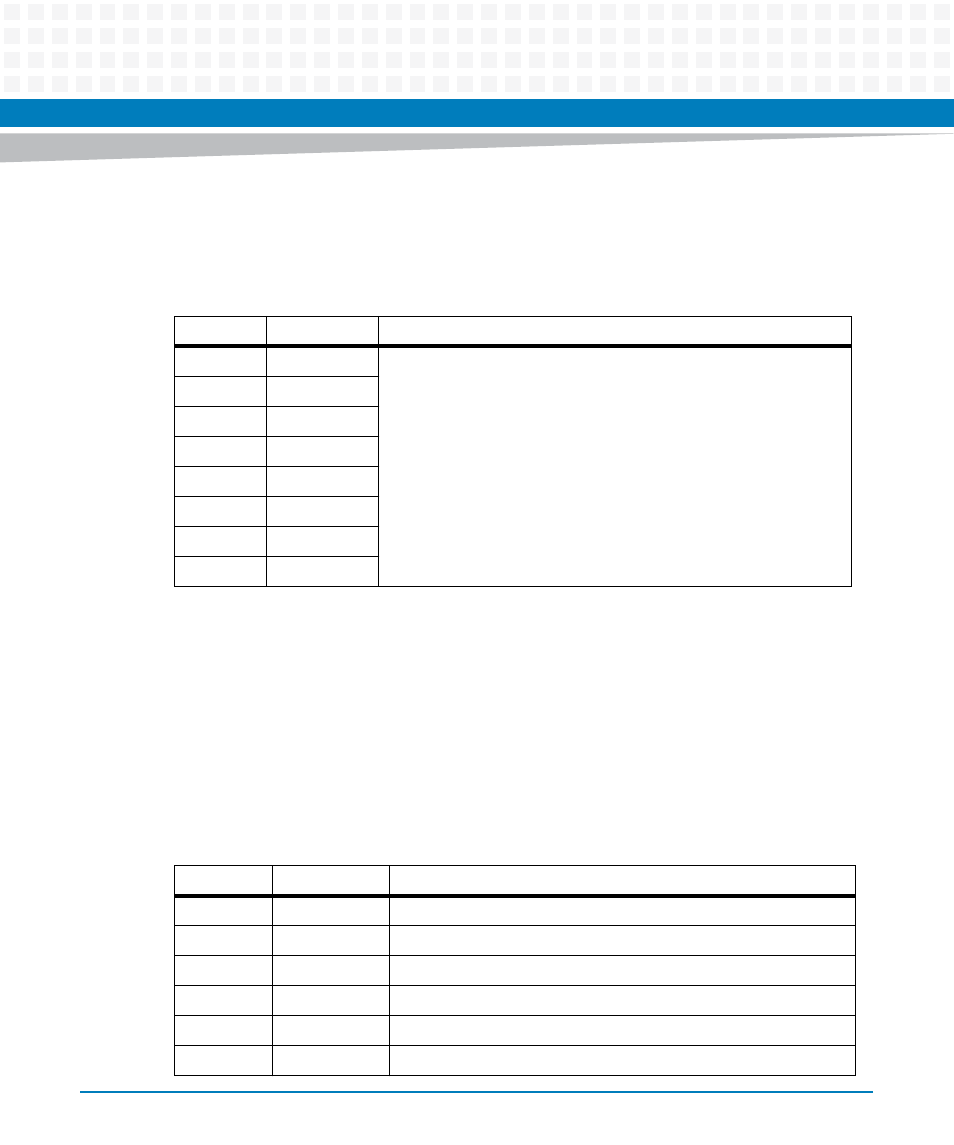

Table 5-4 PLD Version (0x08)

Bits

Function

Description

7

0

This is hard coded in the PLD and changes with every released code

change. Version starts at 00

16

.

6

0

5

0

4

0

3

0

2

0

1

0

0

0

Table 5-5 PLL Reset Configuration (0x0C)

Bits

Function

Description

7

reserved

6

CCCB2

CCB2 to CORE clock ratio

5

CCCB1

CCB1 to CORE clock ratio

4

CCCB0

CCB0 to CORE clock ratio

3

CCBSYS3

SYSCLOCK3 to CCB clock ratio

2

CCBSYS2

SYSCLOCK2 to CCB clock ratio