AMD Geode LX [email protected] User Manual

Page 672

672

AMD Geode™ LX Processors Data Book

Instruction Set

33234H

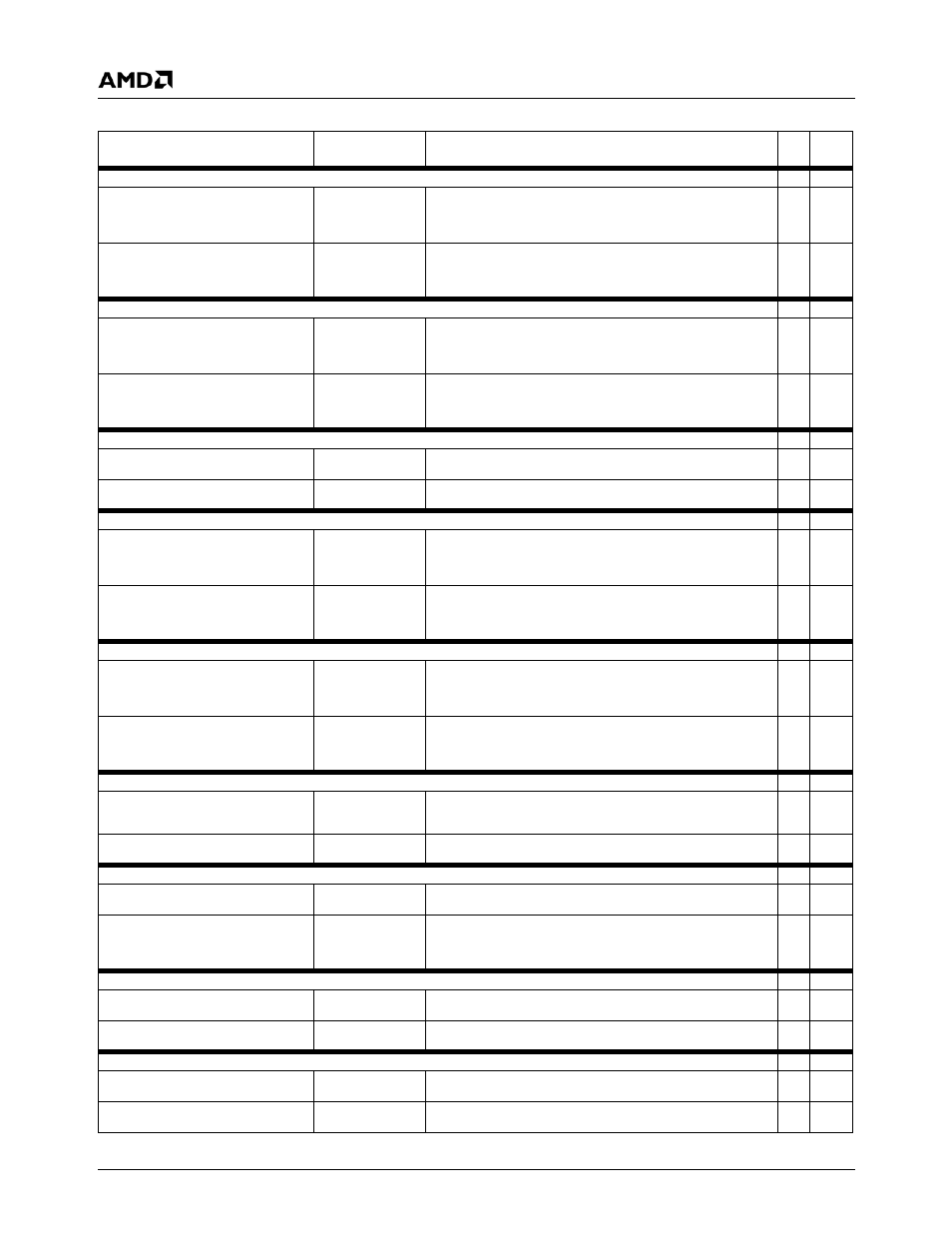

PFMAX Packed Floating-Point MAXimum

2

MMX Register1 with MMX Register2

0F0F [11 mm1

mm2] A4

MMX reg 1[dword] <--- MMX reg 1 [dword] --- if (MMX reg 1 [dword]

>

MMX reg 2 [dword])

MMX reg 1 [dword] <--- MMX reg 2 [dword] --- if (MMX reg 1 [dword]

NOT

>

MMX reg 2 [dword])

MMX Register with Memory64

0F0F [mod mm r/m]

A4

MMX reg [dword] <--- MMX reg [dword] --- if (MMX reg [dword]

>

Memory64 [dword])

MMX reg [dword] <--- Memory [dword --- if (MMX reg [dword] NOT

>

Memory64 [dword])

PFMIN Packed Floating - Point MINimum

2

MMX Register 1 with MMX Register2

0F0F [11 mm1

mm2] 94

MMX reg 1 [dword] <--- MMX reg 1 [dword] --- if (MMX reg 1 [dword]

<

MMX reg 2 [dword])

MMX reg 1 [dword] <--- MMX reg 1 [dword] --- if (MMX reg 1 [dword]

NOT

<

MMX reg 2 [dword])

MMX register1 with Mwnory64

0F0F [mod mm r/m]

94

MMX reg [dword] <--- MMX reg [dword] --- if (MMX reg [dword]

<

Memory64 [dword])

MMX reg [dword] <--- Memory64 [dword] --- if (MMX reg [dword] NOT

<

Memory64 [dword])

PFMUL Packed Floating-Point Multiplication

2

MMX Register 1 with MMX Register 2

0F0F [11 mm1

mm2] B4

MMX reg 1 [dword] <--- sat --- MMX reg 1 [dword] * MMX reg 2 [dword]

MMX Register with Memory64

0F0F [mod mm 2]

B4

MMX reg [dword] <--- sat --- MMX reg [dword] * Memory64 [dword]

PFNACC Packed Floating-Point Negative Accumulate

2

MMX Register1 with MMX Register2

0F0F [11 mm1

mm2] 8A

MMX reg 1 [low dword] <--- (MMX reg 1 [low dword] - MMX reg 1 [high

dword])

MMX reg 1 [high dword] <--- (MMX reg 2 [low dword] - MMX reg 2 [high

dword])

MMX Register with Memory64

0F0F [mod mm r/m]

8A

MMX reg [low dword] <--- (MMX reg [low dword] - MMX reg [high

dword])

MMX reg [high dword] <--- (Memory64 [low dword] - Memory64 [high

dword])

PFPNACC Packed Floating-Point Mixed Positive-Negative Accumulate

2

MMX Register1 with MMX Register2

0F0F [11 mm1

mm2] 8E

MMX reg 1 [low dword] <--- (MMX reg 1 [low dword] - MMX reg 1 [high

dword])

MMX reg 1 [high dword] <--- (MMX reg 2 [low dword] + MMX reg 2

[high dword])

MMX Register with Memory64

0F0F [mod mm r/m]

8E

MMX reg [low dword] <--- (MMX reg [low dword] - MMX reg [low

dword])

MMX reg [high dword] <--- (Memory64 [low dword] - Memory64 [high

dword])

PFRCP Floating-Point Reciprocal Approximation

2

1

MMX Register1 with MMX Register2

0F0F [11 mm1

mm2] 96

MMX reg 1 [low dword] <--- sat --- reciprocal --- MMX reg 2 [low dword]

MMX reg 1 [high dword] <--- sat --- reciprocal --- MMX reg 2 [low

dword]

MMX Register with Memory64

0F0F [mod mm r/m]

96

MMX reg [Low dword] <--- sat --- reciprocal --- Memory64 [low dword]

MMX reg [high dword] <--- sat --- reciprocal --- Memory64 [low dword]

PFRCPV Floating-Point Reciprocal Vector

2

3

MMX Register1 with MMX Register

0F0F [11 mm1

mm2] 86

MMX reg 1 [low dword] <---sat --- reciprocal --- MMX reg 2 [low dword]

MMX reg 1 [high dword] <--- sat --- reciprocal MMX reg 2 [high dword]

MMX Register with Memory64

0F0F [mod mm r/m]

86

MMX reg [low dword] <---sat --- reciprocal Value - Memory64 [low

dword]

MMX reg [high dword] <--- sat --- reciprocal value - Memory64 [high

dword]

PFRCPIT1 Packed Floating-Point Reciprocal, First Iteration Step

1

1, 2

MMX Register1 with MMX Register 2

0F0F [11 mm1

mm2] A6

MMX reg 1 [dword] <--- move --- MMX reg 2 [dword]

MMX Register with Memory64

0F0F [mod mm r/m]

A6

MMX reg [dword] <-- move --- Memory64 [dword]

PFRCPIT2 Packed Floating-Point Reciprocal/Reciprocal Square Root, Second Iteration Step

1

1, 2

MMX Register 1 with MMX Register 2

0FDF [11 mm1

mm2] B6

MMX reg 1 [dword] <--- move --- MMX reg 2 [dword]

MMX Register with Memory64

0FDF [mod mm r/m]

B6

MMX reg [dword] <--- move --- Memory64 [dword]

Table 8-30. AMD 3DNow!™ Technology Instruction Set (Continued)

AMD 3DNow!™ Instructions

Opcode/imm8

Operation

Clk

Cnt

Notes