Table 8-28, Mmx™ instruction set, Table 8-28. th – AMD Geode LX [email protected] User Manual

Page 660: Table 8-28. mmx™ instruction set

660

AMD Geode™ LX Processors Data Book

Instruction Set

33234H

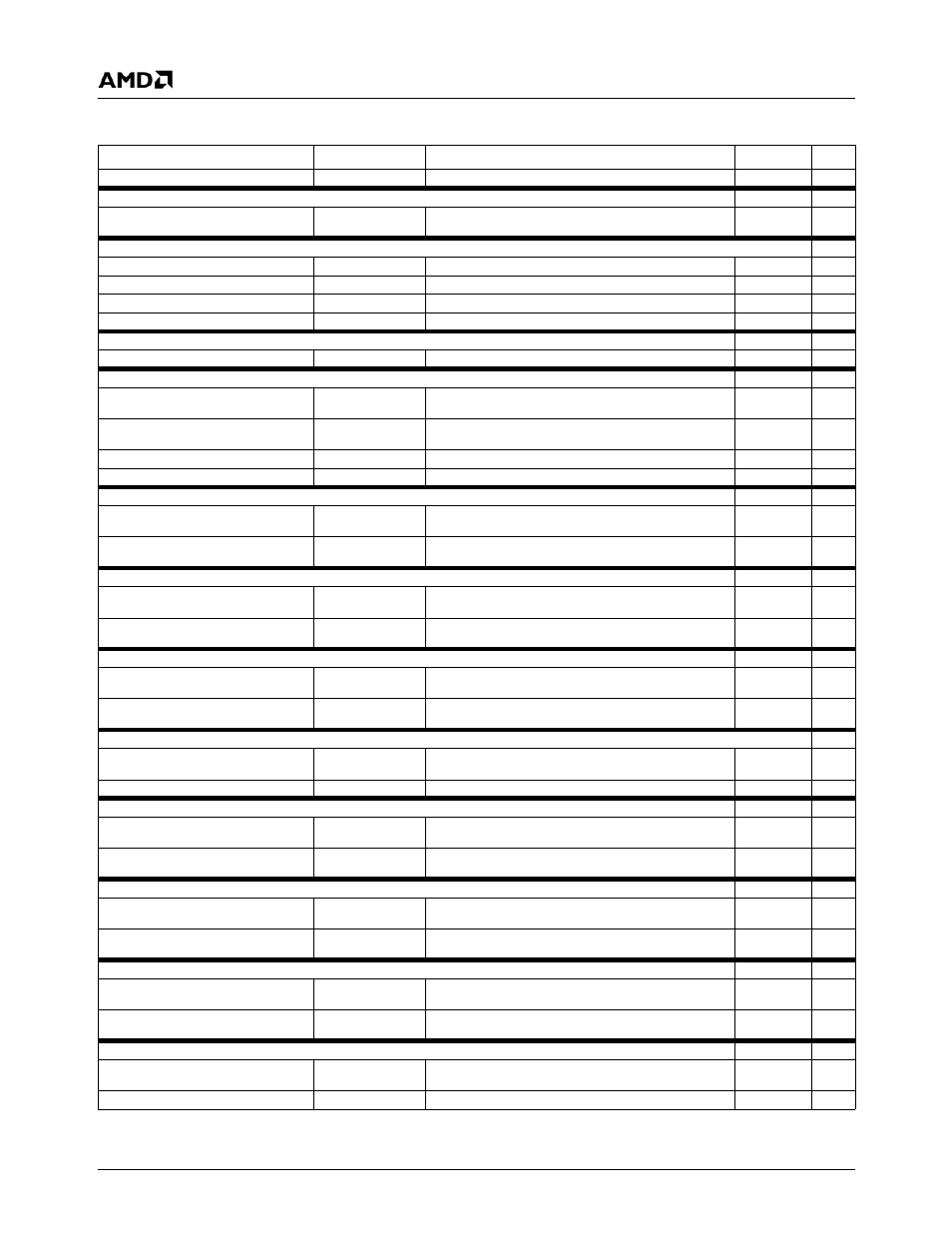

Table 8-28. MMX™ Instruction Set

MMX™ Instructions

Opcode

Operation

Clock Ct

Notes

EMMS Empty MMX State

0F77

Tag Word <--- FFFFh (empties the floating point tag word)

1

1

MASKMOVQ Streaming (Cache Bypass) Store Using Byte Mask (Using EDI Register)

2

MMX Register1with MMX Register2

0FF7 [11 mm1

mm2]

memory [edi] [byte] <--- MMX reg 2 [Sign byte] ? MMX reg 1

[byte] : memory [edi] [byte]

MOVD Move Doubleword

Register to MMX Register

0F6E [11 mm reg]

MMX reg [qword] <--- zero extend --- reg [dword]

1

MMX Register to Register

0F7E [11 mm reg]

reg [qword] <--- MMX reg [low dword]

1

Memory to MMX Register

0F6E [mod mm r/m]

MMX regr [qword] <--- zero extend --- memory [dword]

1

MMX Register to Memory

0F7E [mod mm r/m]

Memory [dword] <--- MMX reg [low dword]

1

MOVNTQ Streaming (Cache Bypass) Store

1

MMX Register to Memory64

0FE7 [mod mm r/m]

Memory64 [qword] <--- MMX reg [qword]

MOVQ Move Quardword

MMX Register 2 to MMX Register 1

0F6F [11 mm1

mm2]

MMX reg 1 [qword] <--- MMX reg 2 [qword]

1

MMX Register 1 to MMX Register 2

0F7F [11 mm1

mm2]

MMX reg 2 [qword] <--- MMX reg 1 [qword]

1

Memory to MMX Register

0F6F [mod mm r/m]

MMX reg [qword] <--- memory[qword]

1

MMX Register to Memory

0F7F [mod mm r/m]

Memory [qword] <--- MMX reg [qword]

1

PACKSSDW Pack Dword with Signed Saturation

MMX Register 2 to MMX Register 1

0F6B [11 mm1

mm2]

MMX reg 1 [qword] <--- packdw, signed sat --- MMX reg 2,

MMX reg 1

2

Memory to MMX Register

0F6B [mod mm r/m]

MMX reg [qword] <--- packdw, signed sat --- memory, MMX

reg

2

PACKSSWB Pack Word with Signed Saturation

MMX Register 2 to MMX Register 1

0F63 [11 mm1 mm2]

MMX reg 1 [qword] <--- packwb, signed sat --- MMX reg 2,

MMX reg 1

2

Memory to MMX Register

0F63 [mod mm r/m]

MMX reg [qword] <--- packwb, signed sat --- memory, MMX

reg

2

PACKUSWB Pack Word with Unsigned Saturation

MMX Register 2 to MMX Register 1

0F67 [11 mm1 mm2]

MMX reg 1 [qword] <--- packwb, unsigned sat --- MMX reg 2,

MMX reg 1

2

Memory to MMX Register

0F67 [mod mm r/m]

MMX reg [qword] <--- packwb, unsigned sat --- memory, MMX

reg

2

PADDB Packed Add Byte with Wrap-Around

MMX Register 2 to MMX Register 1

0FFC [11 mm1

mm2]

MMX reg 1 [byte] <--- MMX reg 1 [byte] + MMX reg 2 [byte]

2

Memory to MMX Register

0FFC [mod mm r/m]

MMX reg[byte] <--- memory [byte] + MMX reg [byte]

2

PADDD Packed Add Dword with Wrap-Around

MMX Register 2 to MMX Register 1

0FFE [11 mm1

mm2]

MMX reg 1 [sign dword] <--- MMX reg 1 [sign dword] + MMX

reg 2 [sign dword]

2

Memory to MMX Register

0FFE [mod mm r/m]

MMX reg [sign dword] <--- memory [sign dword] + MMX reg

[sign dword]

2

PADDSB Packed Add Signed Byte with Saturation

MMX Register 2 to MMX Register 1

0FEC [11 mm1

mm2]

MMX reg 1 [sign byte] <--- sat --- (MMX reg 1 [sign byte] +

MMX reg 2 [sign byte])

2

Memory to Register

0FEC [mod mm r/m]

MMX reg [sign byte] <--- sat --- (memory [sign byte] + MMX

reg [sign byte])

2

PADDSW Packed Add Signed Word with Saturation

MMX Register 2 to MMX Register 1

0FED [11 mm1

mm2]

MMX reg 1 [sign word] <--- sat --- (MMX reg 1 [sign word] +

MMX reg 2 [sign word])

2

Memory to Register

0FED [mod mm r/m]

MMX reg [sign word] <--- sat --- (memory [sign word] + MMX

reg [sign word])

2

PADDUSB Add Unsigned Byte with Saturation

MMX Register 2 to MMX Register 1

0FDC [11 mm1

mm2]

MMX reg 1 [byte] <--- sat --- (MMX reg 1 [byte] + MMX reg 2

[byte])

2

Memory to Register

0FDC [mod mm r/m]

MMX reg [byte] <--- sat --- (memory [byte] + MMX reg [byte])

2