3 performance event counter 1 msr (perf_cnt1_msr), 000000c2h, Performance event counter 1 msr (perf_cnt1_msr) – AMD Geode LX [email protected] User Manual

Page 111: 00000000_00000000h

AMD Geode™ LX Processors Data Book

111

CPU Core Register Descriptions

33234H

5.5.2.3

Performance Event Counter 1 MSR (PERF_CNT1_MSR)

MSR Address

000000C2h

Type

R/W

Reset Value

00000000_00000000h

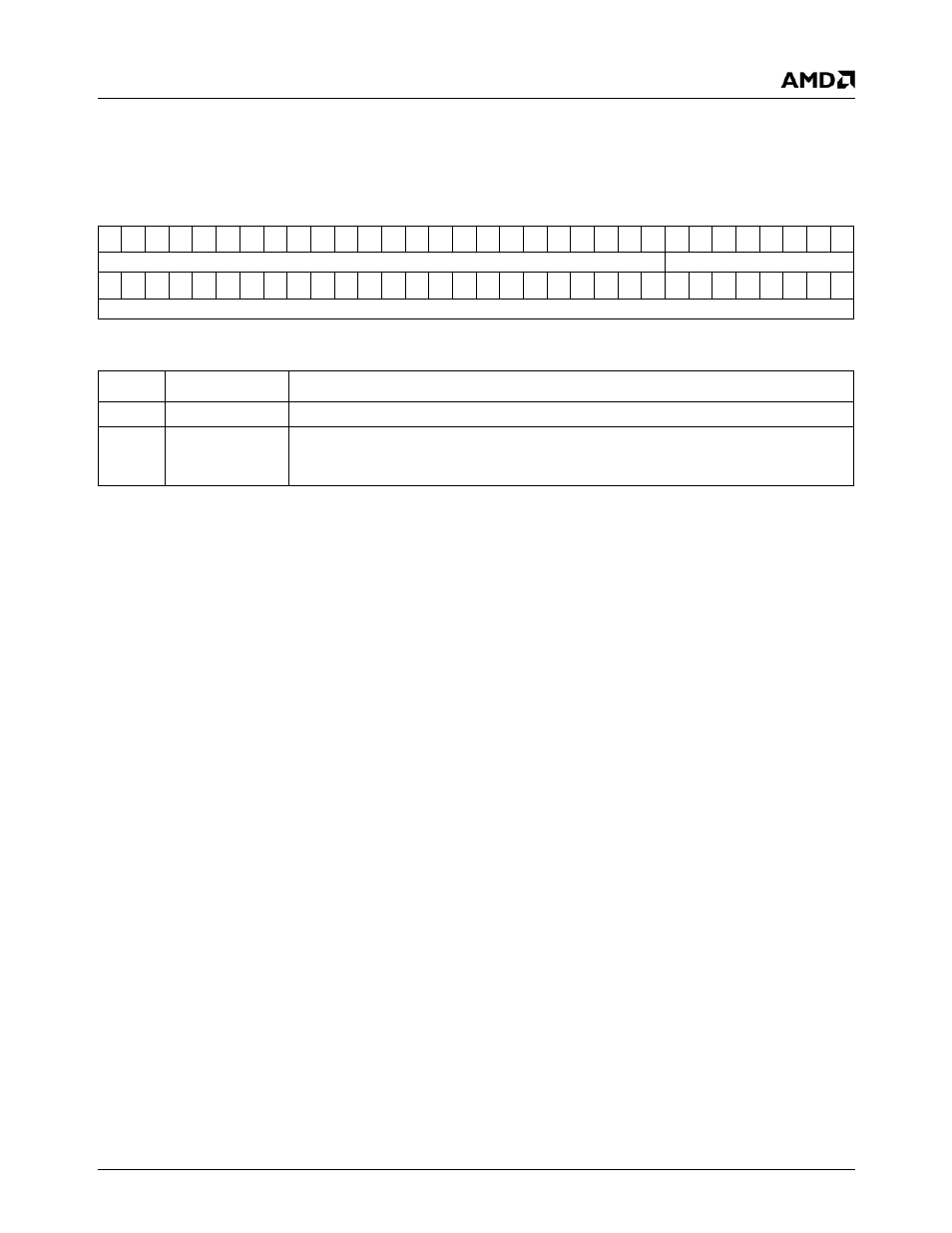

PERF_CNT1_MSR Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

PERF_CNT1 (High Byte)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

PERF_CNT1 (Low DWORD)

PERF_CNT1_MSR Bit Descriptions

Bit

Name

Description

63:40

RSVD

Reserved. Write as read.

39:0

PERF_CNT1

Performance Event Counter 1. This register is a 40-bit event counter used to count

events or conditions inside the CPU Core. This counter is controlled by Performance

Event Counter 1 Select MSR (MSR 00000187h).

This manual is related to the following products: