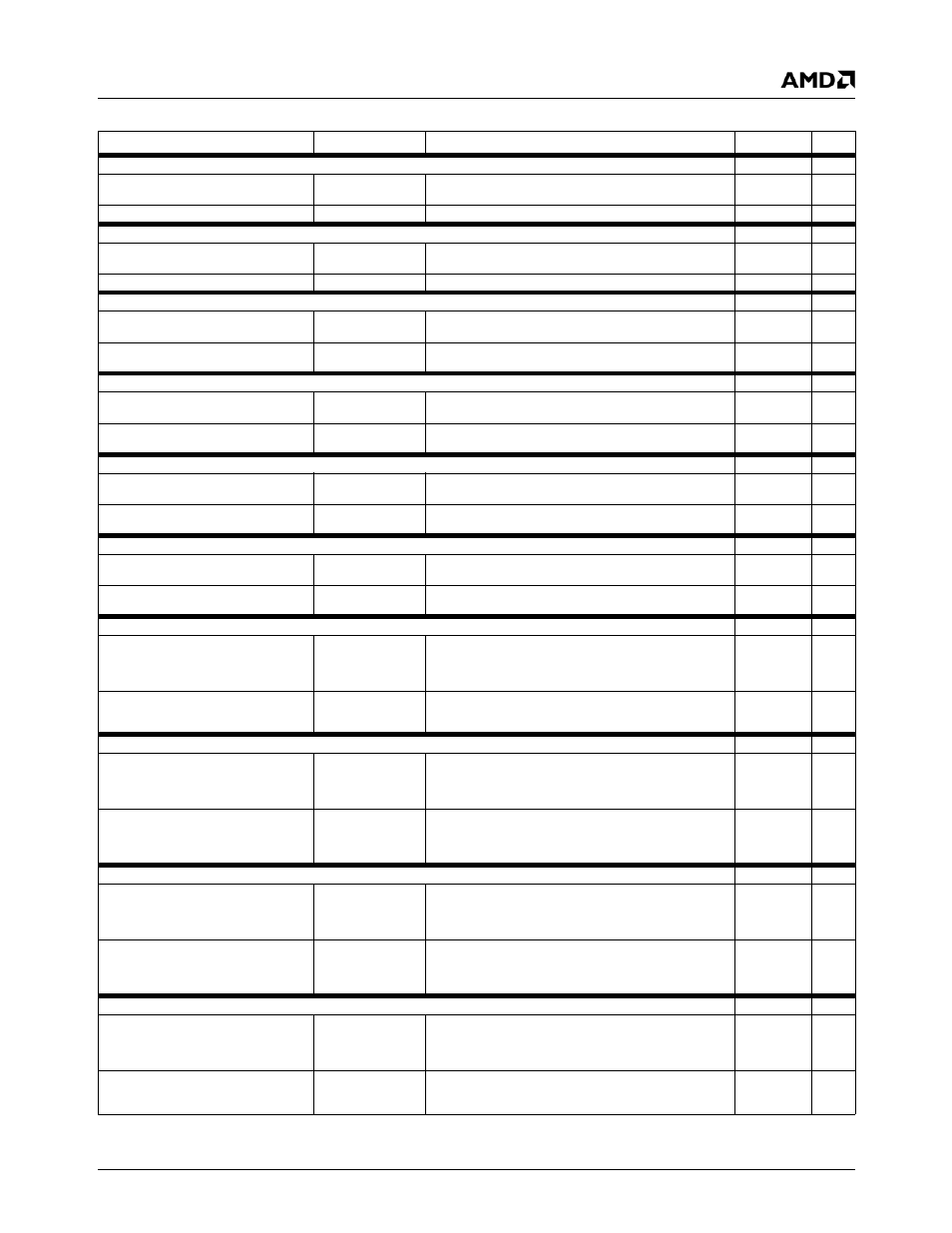

Table 8-28. mmx™ instruction set (continued) – AMD Geode LX [email protected] User Manual

Page 661

AMD Geode™ LX Processors Data Book

661

Instruction Set

33234H

PADDUSW Add Unsigned Word with Saturation

MMX Register 2 to MMX Register 1

0FDD [11 mm1

mm2]

MMX reg 1 [word] <--- sat --- (MMX reg 1 [word] + MMX reg 2

[word])

2

Memory to Register

0FDD [mod mm r/m]

MMX reg [word] <--- sat --- (memory [word] + MMX reg [word])

2

PADDW Packed Add Word with Wrap-Around

MMX Register 2 to MMX Register 1

0FFD [11 mm1

mm2]

MMX reg 1 [word] <--- MMX reg 1 [word] + MMX reg 2 [word]

2

Memory to MMX Register

0FFD [mod mm r/m]

MMX reg [word] <--- memory [word] + MMX reg [word]

2

PAND Bitwise Logical AND

MMX Register 2 to MMX Register 1

0FDB [11 mm1

mm2]

MMX reg 1 [qword] --- MMX reg 1 [qword], <--- logic AND ---

MMX reg 2 [qword]

2

Memory to MMX Register

0FDB [mod mm r/m]

MMX reg [qword] memory [qword], <--- logic AND --- MMX reg

[qword]

2

PANDN Bitwise Logical AND NOT

MMX Register 2 to MMX Register 1

0FDF [11 mm1

mm2]

MMX reg 1 [qword] NOT (MMX reg 1 [qword], <--- logic AND

--- MMX reg 2) [qword]

2

Memory to MMX Register

0FDF [mod mm r/m]

MMX reg [qword] --- NOT (MMX reg [qword], <--- logic AND

--- Memory [qword])

2

PAVGB Packed Average of Unsigned Byte

MMX Register 1 with MMX Register 2

0FE0 [11 mm1

mm2]

MMX reg 1 [byte] <--- round up --- (MMX reg 1 [byte] + MMX

reg 2 [byte] + 01h)/2

2

MMX Register with Memory64

0FE0 [mod mm r/m]

MMX reg 1 [byte] <--- round up --- (MMX reg 1 [byte] +

Memory64 [byte] + 01h)/2

2

PAVGW Packed Average of Unsigned Word

MMX Register 1 with MMX Register 2

0FE3 [11 mm1

mm2]

MMX reg 1 [word] <--- round up --- (MMX reg 1[word] + MMX

reg 2 [word] + 01h)/2

2

MMX Register with Memory

0FE3 [mod mm r/m]

MMX reg 1[word] <--- round up --- (MMX reg, [word] +

Memory64 [word] + 01h)/2

2

PCMPEQB Packed Byte Compare for Equality

MMX Register 2 with MMX Register 1

0F74 [11 mm1 mm2]

MMX reg 1 [byte] <--- FFh --- if MMX reg 1 [byte] = MMX reg 2

[byte]

MMX reg 1 [byte]<--- 00h --- if MMX reg 1 [byte] NOT = MMX

reg 2 [byte]

2

Memory with MMX Register

0F74 [mod mm r/m]

MMX reg [byte] <--- FFh --- if memory[byte] = MMX reg [byte]

MMX reg [byte] <--- 00h --- if memory[byte] NOT = MMX reg

[byte]

2

PCMPEQD Packed Dword Compare for Equality

MMX Register 2 with MMX Register 1

0F76 [11 mm1 mm2]

MMX reg 1 [dword] <--- FFFF FFFFh --- if MMX reg 1 [dword]

= MMX reg 2 [dword]

MMX reg 1 [dword]<--- 0000 0000h ---if MMX reg 1[dword]

NOT = MMX reg 2 [dword]

2

Memory with MMX Register

0F76 [mod mm r/m]

MMX reg [dword] <--- FFFF FFFFh --- if memory[dword] =

MMX reg [dword]

MMX reg [dword] <--- 0000 0000h --- if memory[dword] NOT

= MMX reg [dword]

2

PCMPEQW Packed Word Compare for Equality

MMX Register 2 with MMX Register 1

0F75 [11 mm1 mm2]

MMX reg 1 [word] <--- FFFFh --- if MMX reg 1 [word] = MMX

reg 2 [word]

MMX reg 1 [word]<--- 0000h --- if MMX reg 1 [word] NOT =

MMX reg 2 [word]

2

Memory with MMX Register

0F75 [mod mm r/m]

MMX reg [word] <--- FFFFh --- if memory[word] = MMX reg

[word]

MMX reg [word] <--- 0000h --- if memory[word] NOT = MMX

reg [word]

2

PCMPGTB Pack Compare Greater Than Byte

MMX Register 2 to MMX Register 1

0F64 [11 mm1 mm2]

MMX reg 1 [byte] <--- FFh --- if MMX reg 1 [byte] > MMX reg 2

[byte]

MMX reg 1 [byte]<--- 00h --- if MMX reg 1 [byte] NOT > MMX

reg 2 [byte]

2

Memory with MMX Register

0F64 [mod mm r/m]

MMX reg [byte] <--- FFh --- if memory[byte] > MMX reg [byte]

MMX reg [byte] <--- 00h --- if memory[byte] NOT > MMX reg

[byte]

2

Table 8-28. MMX™ Instruction Set (Continued)

MMX™ Instructions

Opcode

Operation

Clock Ct

Notes