AMD Geode LX [email protected] User Manual

Page 641

AMD Geode™ LX Processors Data Book

641

Instruction Set

33234H

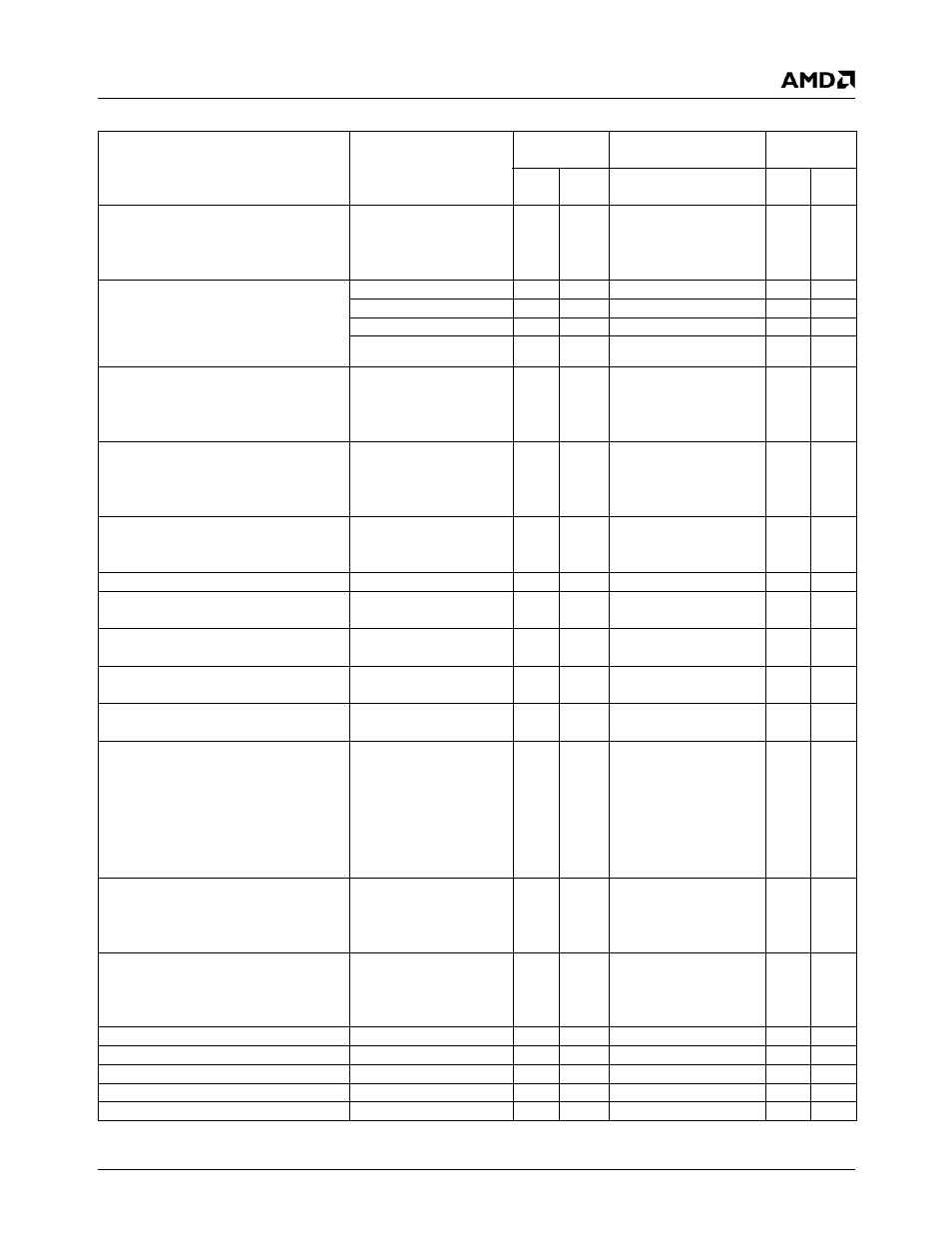

REP CMPS

CX==0

6

6

CX==1

13

13

CX>1

10+3C

10+3C

REP INS Input String

F3 6[110w]

-

-

-

-

-

-

-

-

-

b

h,m

CX==0

9

9/24

CX==1

CX>1

15+6C

15+6C/

30+6C

REP LODS Load String

F3 A[110w]

-

-

-

-

-

-

-

-

-

b

h

CX==0

5

5

CX==1

10

10

CX>1

8+2C

8+2C

REP MOVS Move String

F3 A[010w]

-

-

-

-

-

-

-

-

-

b

h

CX==0

5

5

CX==1

13

13

CX>1

11+2C

11+2C

REP OUTS Output String

F3 6[111w]

16+10

C

16+10

C\

31+10

C

-

-

-

-

-

-

-

-

-

b

h,m

REP STOS Store String

F3 A[101w]

8+c

8+c

-

-

-

-

-

-

-

-

-

b

h

REPE CMPS Compare String

Find non-match

F3 A[011w]

11+4n

11+4n

x

-

-

-

x

x

x

x

x

b

h

REPE SCAS Scan String

Find non-AL/AX/EAX

F3 A[111w]

7+2n

7+2n

x

-

-

-

x

x

x

x

x

b

h

REPNE CMPS Compare String

Find match

F2 A[011w]

10+4n

10+4n

x

-

-

-

x

x

x

x

x

b

h

REPNE SCAS Scan String

Find AL/AX/EAX

F2 A[111w]

7+3n

7+3n

x

-

-

-

x

x

x

x

x

b

h

RET Return from Subroutine

-

-

-

-

-

-

-

-

-

Within Segment

C3

3

3

b

g,h,j,k,

r

Within Segment Adding Immediate to SP

C2 ##

3

3

Intersegment

CB

6

10-48

Intersegment Adding Immediate to SP

CA ##

7

10-48

Protected Mode: Different Privilege Level

-Intersegment

-Intersegment Adding Immediate to SP

35

35

ROL Rotate Left

Register/Memory by 1

D[000w] [mod 000 r/m]

2

2

x

-

-

-

-

-

-

-

x

b

h

Register/Memory by CL

D[001w] [mod 000 r/m]

2

2

u

-

-

-

-

-

-

-

x

Register/Memory by Immediate

C[000w] [mod 000 r/m] #

2

2

u

-

-

-

-

-

-

-

x

ROR Rotate Right

Register/Memory by 1

D[000w] [mod 001 r/m]

2

2

x

-

-

-

-

-

-

-

x

b

h

Register/Memory by CL

D[001w] [mod 001 r/m]

2

2

u

-

-

-

-

-

-

-

x

Register/Memory by Immediate

C[000w] [mod 001 r/m] #

2

2

u

-

-

-

-

-

-

-

x

RSDC Restore Segment Register and Descriptor

0F 79 [mod sreg3 r/m]

9

9

-

-

-

-

-

-

-

-

-

s,u

s,u

RSLDT Restore LDTR and Descriptor

0F 7B [mod 000 r/m]

9

9

-

-

-

-

-

-

-

-

-

s,u

s,u

RSTS Restore TSR and Descriptor

0F 7D [mod 000 r/m]

10

10

-

-

-

-

-

-

-

-

-

s,u

s,u

RSM Resume from SMM Mode

0F AA

35

35

x

x

x

x

x

x

x

x

x

s,u

s,u

SAHF Store AH in FLAGS

9E

1

1

-

-

-

-

x

x

x

x

x

Table 8-26. Processor Core Instruction Set (Continued)

Instruction

Opcode

Clock Count

(Reg/Cache Hit)

Flags

Notes

Real

Mode

Prot’d

Mode

O D I

T

S Z

A P C

F

F

F

F

F

F

F

F

F

Real

Mode

Prot’d

Mode