2 gliu register descriptions, Gliu register descriptions, Table 4-5 – AMD Geode LX [email protected] User Manual

Page 50: Table 4-6, Gliu specific msrs summary

50

AMD Geode™ LX Processors Data Book

GLIU Register Descriptions

33234H

4.2

GLIU Register Descriptions

All GeodeLink™ Interface Unit (GLIU) registers are Model

Specific Registers (MSRs) and are accessed through the

RDMSR and WRMSR instructions.

The registers associated with the GLIU are the Standard

GeodeLink Device (GLD) MSRs, GLIU Specific MSRs.

GLIU Statistic and Comparator MSRs,

P2D Descriptor

MSRs, and I/O Descriptor MSRs. The tables that follow are

register summary tables that include reset values and page

references where the bit descriptions are provided.

Note:

The MSR address is derived from the perspective

of the CPU Core. See Section 4.1 "MSR Set" on

page 45 for more details on MSR addressing.

Reserved (RSVD) fields do not have any meaningful stor-

age elements. They always return 0.

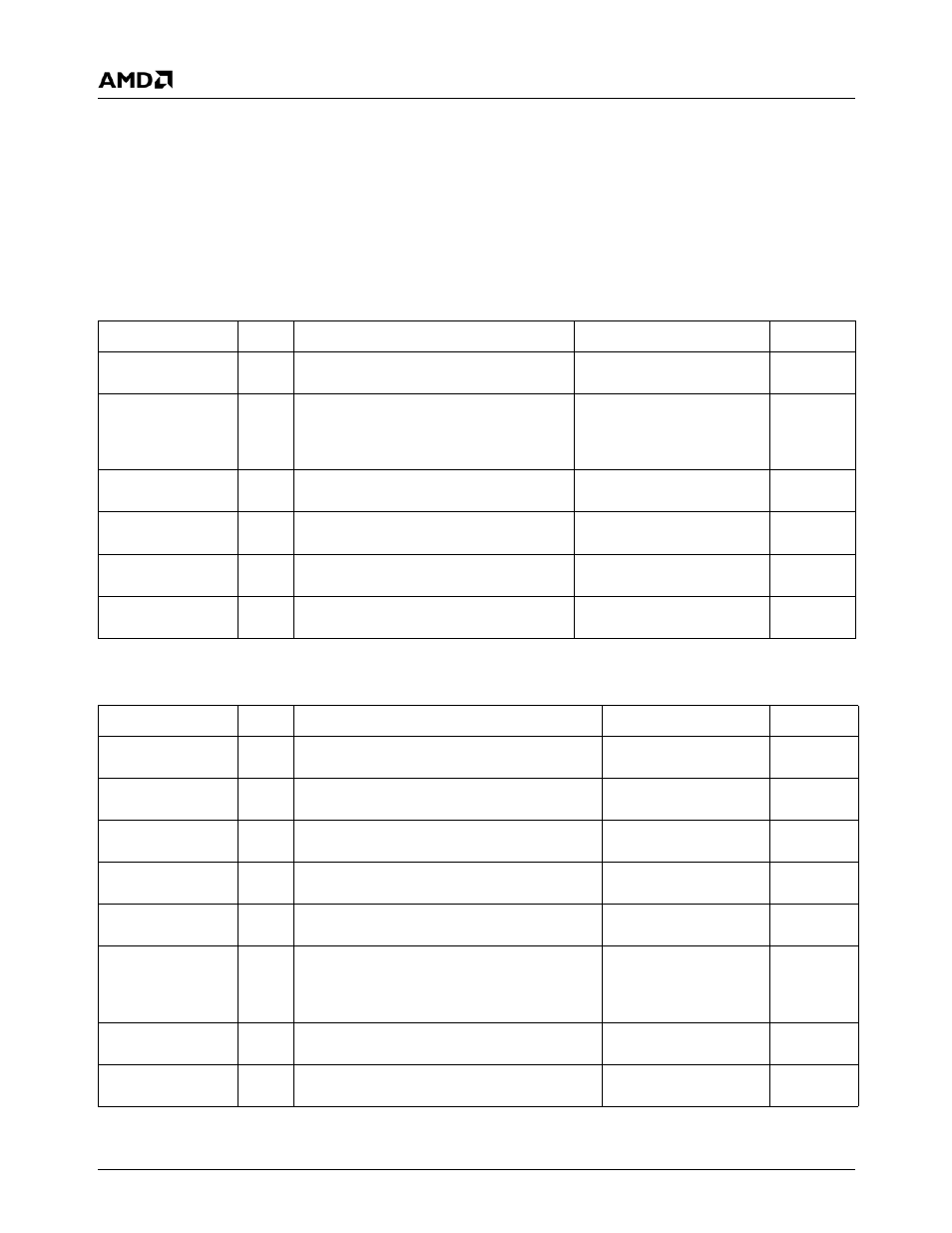

Table 4-5. GeodeLink™ Device Standard MSRs Summary

MSR Address

Type

Register Name

Reset Value

Reference

GLIU0: 10002000h

GLIU1: 40002000h

RO

GLD Capabilities MSR (GLD_MSR_CAP)

00000000_000014xxh

Page 55

GLIU0: 10002001h

GLIU1: 40002001h

R/W

GLD Master Configuration MSR

(GLD_MSR_CONFIG)

GLIU0:

00000000_00000002h

GLIU1:

00000000_00000004h

Page 55

GLIU0: 10002002h

GLIU1: 40002002h

R/W

00000000_00000001h

Page 56

GLIU0: 10002003h

GLIU1: 40002003h

R/W

00000000_00000000h

Page 57

GLIU0: 10002004h

GLIU1: 40002004h

R/W

GLD Power Management MSR

(GLD_MSR_PM)

00000000_00000000h

Page 59

GLIU0: 10002005h

GLIU1: 40002005h

R/W

GLD Diagnostic MSR (GLD_MSR_DIAG)

00000000_00000000h

Page 60

Table 4-6. GLIU Specific MSRs Summary

MSR Address

Type

Register Name

Reset Value

Reference

GLIU0: 10000080h

GLIU1: 40000080h

GLIU0: 10000081h

GLIU1: 40000081h

GLIU0: 10000082h

GLIU1: 40000082h

GLIU0: 10000083h

GLIU1: 40000083h

GLIU0: 10000084h

GLIU1: 40000084h

GLIU0: 10000086h

GLIU1: 40000086h

GLIU Physical Capabilities (PHY_CAP)

GLIU0:

20291830_010C1086h

GLIU1:

20311030_0100400Ah

Page 65

GLIU0: 10000087h

GLIU1: 40000087h

N Outstanding Response (NOUT_RESP)

GLIU0: 10000088h

GLIU1: 40000088h