2 cpuid instruction set, 1 standard cpuid levels, 1 cpuid instruction with eax = 00000000h – AMD Geode LX [email protected] User Manual

Page 627: 2 cpuid instruction with eax = 00000001h, Cpuid instruction set, Table 8-16, Cpuid instruction with eax = 00000000h, Table 8-17, Cpuid instruction with eax = 00000001h

AMD Geode™ LX Processors Data Book

627

Instruction Set

33234H

8.2

CPUID Instruction Set

The CPUID instruction (opcode 0FA2) allows software to make processor inquiries as to the vendor, family, model, step-

ping, features, and specific cache organization information. The presence of support for the CPUID instruction is indicated

by the ability to change the value of the ID flag, bit 21, in the EFLAGS register.

The CPUID level allows the CPUID instruction to return different information in EAX, EBX, ECX, and EDX registers. The

level is determined by the initialized value of the EAX register prior to execution of the CPUID instruction.

8.2.1

Standard CPUID Levels

The standard CPUID levels are part of the standard x86 instruction set.

8.2.1.1

CPUID Instruction with EAX = 00000000h

Standard function 00000000h (EAX = 00000000h) of the CPUID instruction returns the maximum standard CPUID levels,

as well as the processor vendor string.

After the instruction is executed, the EAX register contains the maximum standard CPUID levels supported. The maximum

standard CPUID level is the highest acceptable value for the EAX register input. This does not include the extended CPUID

levels.

The EBX through EDX registers contain the vendor string of the processor as shown in Table 8-16.

8.2.1.2

CPUID Instruction with EAX = 00000001h

Standard function 00000001h (EAX = 00000001h) of the CPUID instruction returns the processor type, family, model, step-

ping information in the EAX register, and the supported standard feature flags in the EDX register. The EBX and ECX reg-

isters are reserved. Table 8-17 provides a register map.

In the EDX register, each flag refers to a specific feature. Some of these features have protection control in CR4. Before

using any of these features, the software should check the corresponding feature flag. Attempting to execute an unavailable

feature can cause exceptions and unexpected behavior. For example, software must check EDX[4] before attempting to use

the Time Stamp Counter instruction.

Table 8-18 on page 628 shows the EAX and EDX bit field formats when EAX = 00000001h and indicates if a feature is not

supported.

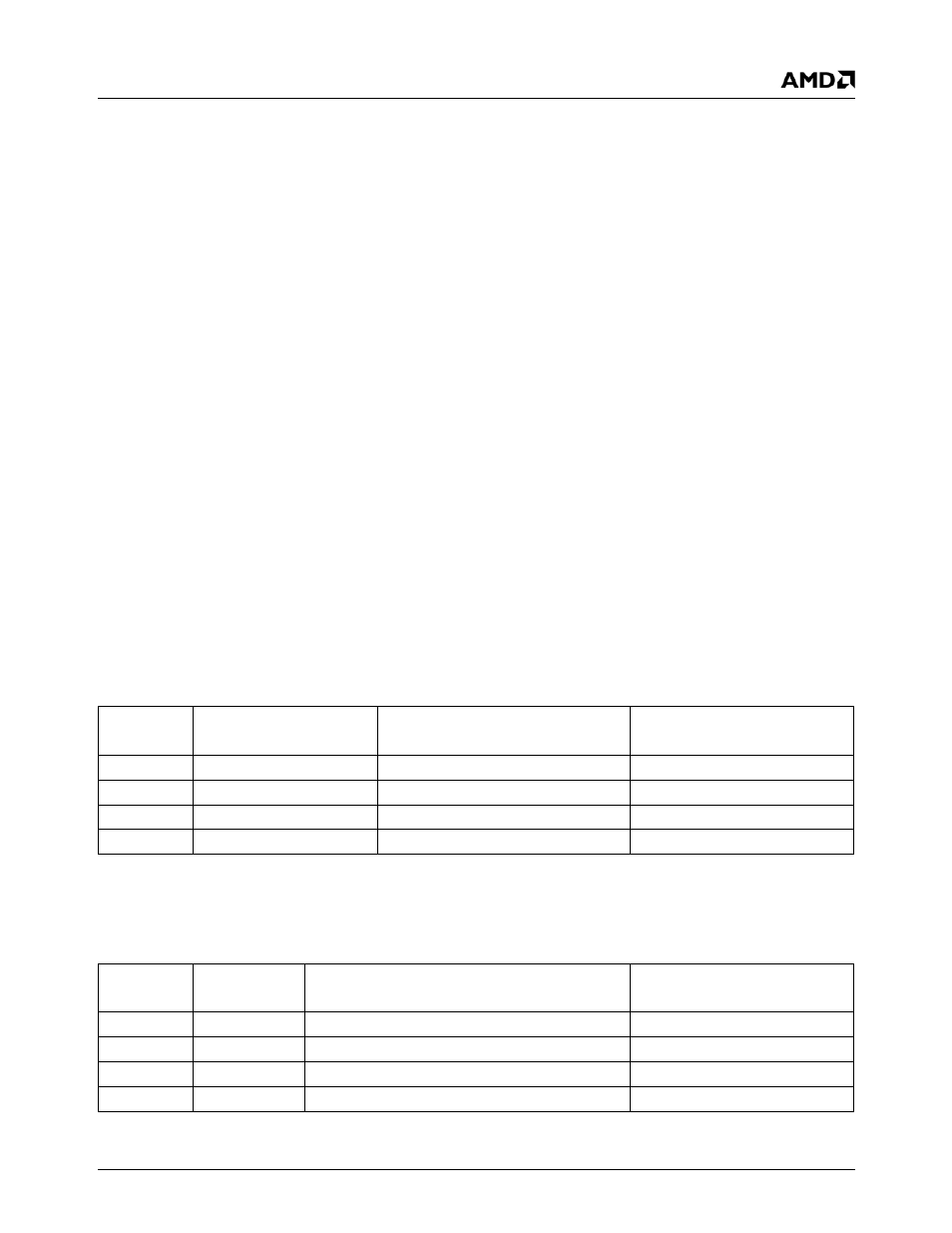

Table 8-16. CPUID Instruction with EAX = 00000000h

Register

(Note 1)

Note 1. The “Register” column is intentionally out of order.

Returned Contents

Description

Comment

EAX

00000001h

Maximum Standard Level

EBX

68747541h

{htuA}

Vendor ID String 1

EDX

69746E65h

{itne}

Vendor ID String 2

ECX

444D4163h

{DMAc}

Vendor ID String 3

Table 8-17. CPUID Instruction with EAX = 00000001h

Register

Returned

Contents

Description

Comment

EAX

000005Axh

Type/Family/Model/Step

EBX

00000400h

Reserved

ECX

00000000h

Reserved

EDX

0088A93Dh

Standard Feature Flags