AMD Geode LX [email protected] User Manual

Page 580

580

AMD Geode™ LX Processors Data Book

GeodeLink™ PCI Bridge Register Descriptions

33234H

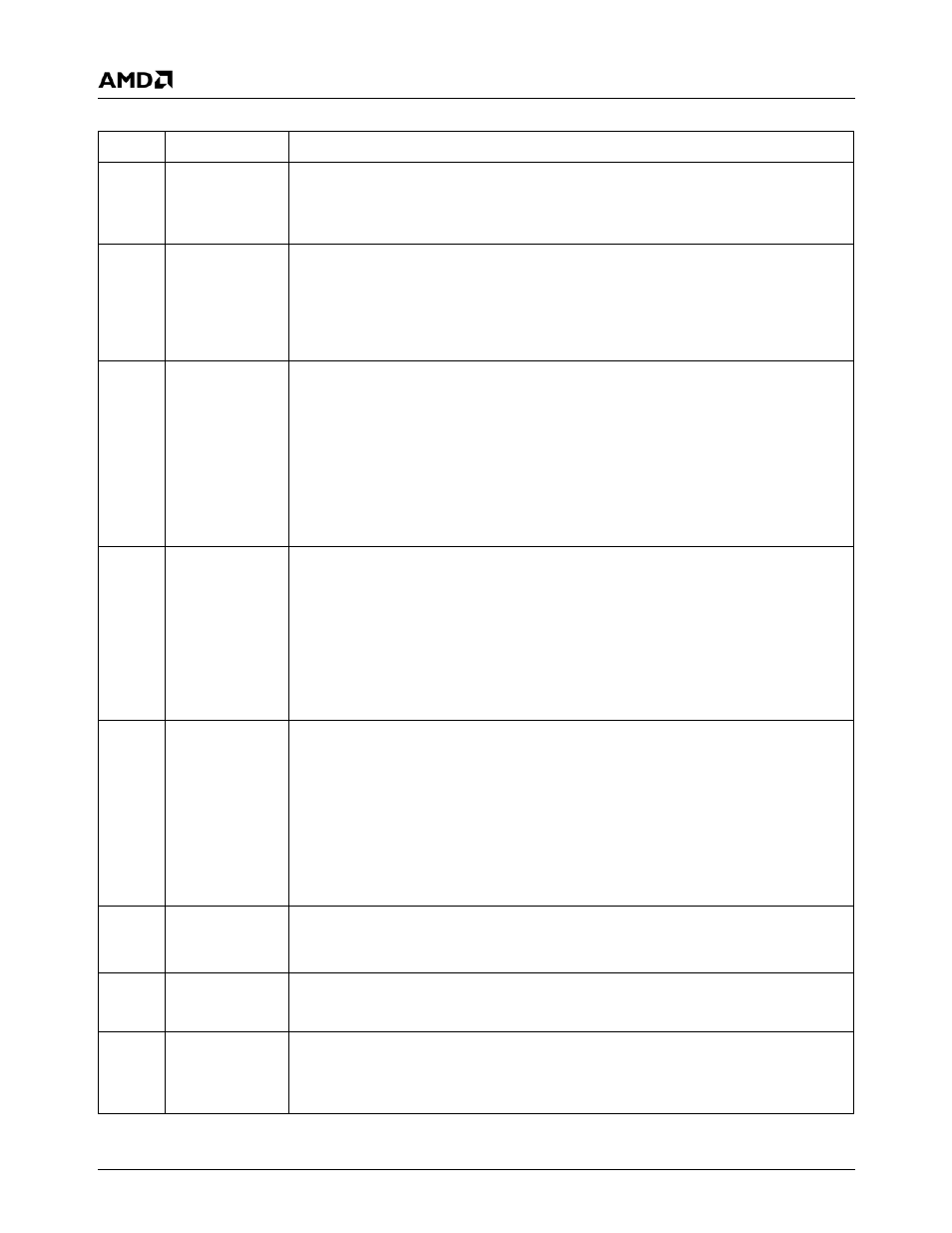

24

MARS

Master Abort Receive ASMI. Allow reception of a PCI bus master abort to be reported

in the TARE bit (MSR 50002002h[17]).

0: Disable.

1: Enable.

23:21

SUS

Busy Sustain. Controls the sustain time for keeping the clocks running after the internal

busy signals indicate that the clocks may be gated.

000: No sustain

100: 32 clock cycles

001: 4 clock cycles

101: 64 clock cycles

010: 8 clock cycles

110: 128 clock cycles

011: 16 clock cycles

111: 256 clock cycles

20:18

IRFT

In-Bound Read Flush Timeout. Controls the flushing of in-bound prefetch read data.

When an in-bound read has completed on the PCI bus, an internal counter is loaded with

a value derived from this field. It then counts down on each PCI clock edge. When the

counter reaches 0, any remaining prefetched data is flushed. The counter stops counting

down if a subsequent in-bound read is received. It continues to count down through an

in-bound write and through any out-bound traffic.

000: 4 PCI clock edge

100: 64 PCI clock edges

001: 8 PCI clock edges

101: 128 PCI clock edges

010: 16 PCI clock edges

110: 256 PCI clock edges

011: 32 PCI clock edges

111: No timeout

17:16

IRFC

In-Bound Read Flush Control. Controls the policy for discarding stale data from in-

bound read data FIFO.

00: Discard at end of in-bound read PCI transaction.

01: Discard upon timeout.

10: Discard at start of out-bound write or upon timeout.

11: Discard at start of out-bound write, at start of out-bound read or upon timeout.

In addition to these policies, in-bound read data will be discarded whenever a non-contig-

uous in-bound read is accepted, or when an in-bound write is received that will affect the

prefetched memory.

15:13

IOD

I/O Delay. Delay completion of out-bound I/O transactions for a configurable number of

PCI clock cycles.

000: 0 PCI clock cycles

001: 1 PCI clock cycles

010: 2 PCI clock cycles

011: 4 PCI clock cycles

100: 8 PCI clock cycles

101: 16 PCI clock cycles

110: 32 PCI clock cycles

111: 64 PCI clock cycles

12

ST

Short Timer. When cleared to 0, delayed transactions are discarded after 2

15

PCI clock

cycles. When set to 1, delayed transactions are discarded after 2

5

PCI clock cycles. For

normal operation. this bit should be cleared.

11

ER

Early Read. When cleared to 0, out-bound reads are stalled until there is enough FIFO

space in the out-bound read FIFO to hold data for the entire transaction. When set to 1,

out-bound reads will start as soon as possible.

10

RHE

Read Hints Enable. When cleared to 0, all out-bound reads use PCI CMD = 6. When set

to 1, the PCI CMD provides a hint about the size of the read request.

6: 1, 2 or 4 DWORDs

E: 8 DWORDs

GLPCI_CTRL Bit Descriptions (Continued)

Bit

Name

Description