6 tft display interface signals – AMD Geode LX [email protected] User Manual

Page 40

40

AMD Geode™ LX Processors Data Book

33234H

3.4.6

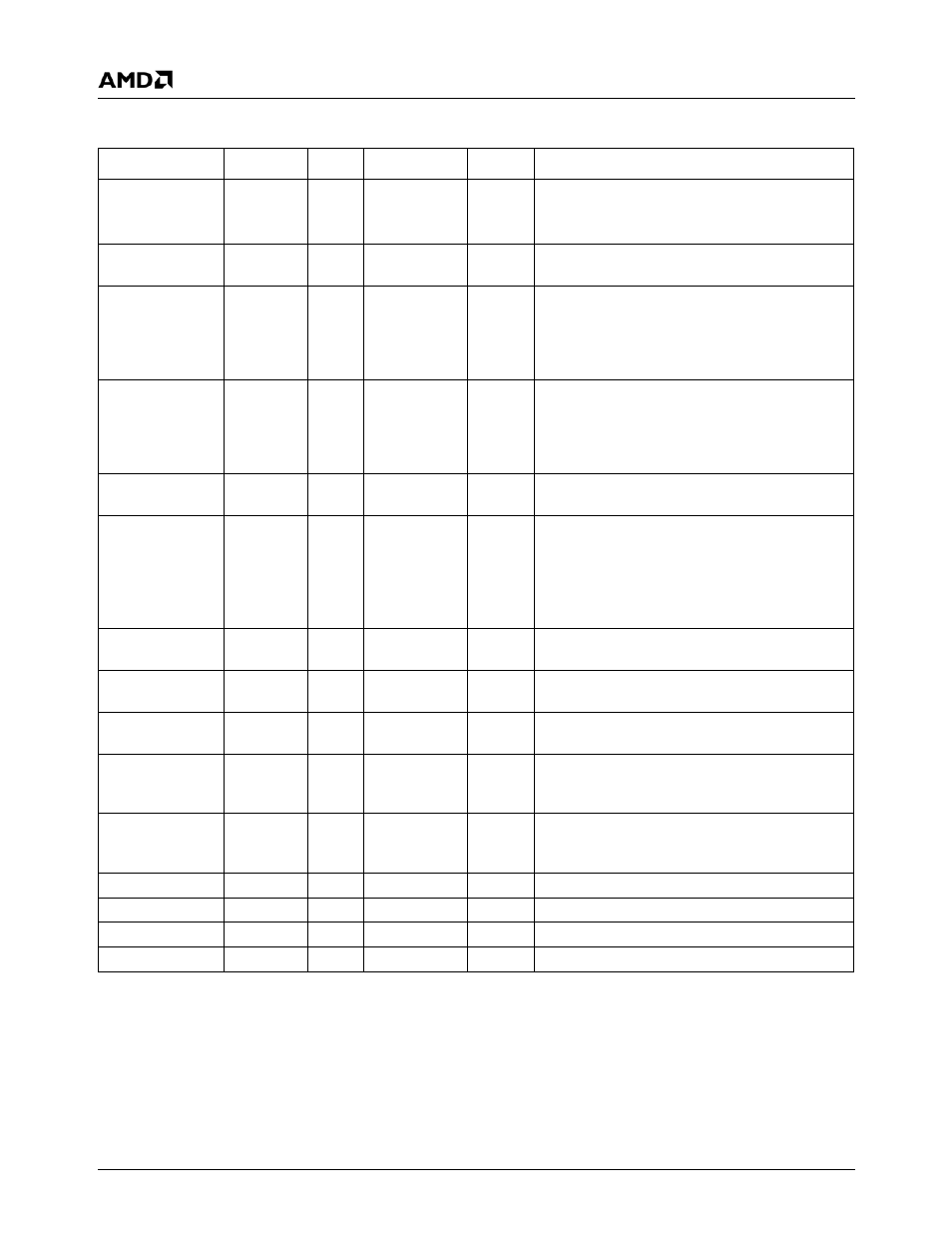

TFT Display Interface Signals

Signal Name

Ball No.

Type

f

V

Description

DRGB[31:24]

DRGB[23:0]

I/O

O

(PD)

0-162 Mb/s

3.3

Display Data Bus.

DOTCLK

AE1

O

(PD)

0-162 MHz

3.3

Dot Clock. Output clock from DOTCLK PLL.

HSYNC

AE3

O

(PD)

0-162 Mb/s

3.3

(5vt)

Horizontal Sync. Horizontal Sync establishes

the line rate and horizontal retrace interval for an

attached flat panel. The polarity is programmable

(See Section 6.8.3.43 on page 451, VP Memory

Offset 400h[29]).

VSYNC

AD3

O

(PD)

0-162 Mb/s

3.3

(5vt)

Vertical Sync. Vertical Sync establishes the

screen refresh rate and vertical retrace interval

for an attached flat panel. The polarity is pro-

grammable (See Section 6.8.3.43 on page 451,

VP Memory Offset 400h[30]).

DISPEN

AE4

O

(PD)

0-162 Mb/s

3.3

Flat Panel Backlight Enable.

VDDEN

AE2

I/O

(PD)

0-162 Mb/s

3.3

LCD VDD FET Control. When this output is

asserted high, V

DD

voltage is applied to the

panel. This signal is intended to control a power

FET to the LCD panel. The FET may be internal

to the panel or not, depending on the panel man-

ufacturer.

LDEMOD

AD4

I/O

(PD)

0-162 Mb/s

3.3

Flat Panel Display Enable (TFT Panels).

MSGSTART

AH11

I

0-75 Mb/s

3.3

Message Start. Used in VIP message passing

mode to indicate start of message.

MSGSTOP

AJ11

I

0-75 Mb/s

3.3

Message Stop. Used in VIP message passing

mode to indicate end of message.

VID[15:8]

I

(PD)

0-75 Mb/s

3.3

Video Input Port Data. When in 16 bit VIP

mode, these are the eight MSBs of the VIP data.

VOP[15:0]

O

0-75 Mb/s

3.3

Video Output Port Data. VOP output data.

VOPCLK

AE1

O

0-75 MHz

3.3

Video Output Port Clock.

VOP_BLANK

AE4

O

0-75 Mb/s

3.3

Video Output Port Blank.

VOP_HSYNC

AE3

O

0-75 Mb/s

3.3

Video Output Port Horizontal Sync.

VOP_VSYNC

AD3

O

0-75 Mb/s

3.3

Video Output Port Vertical Sync.