4 non-standard processor core instructions, 1 dmint - enter debug management mode – AMD Geode LX [email protected] User Manual

Page 646

646

AMD Geode™ LX Processors Data Book

Instruction Set

33234H

8.3.4

Non-Standard Processor Core Instructions

8.3.4.1

DMINT - Enter Debug Management Mode

Operation

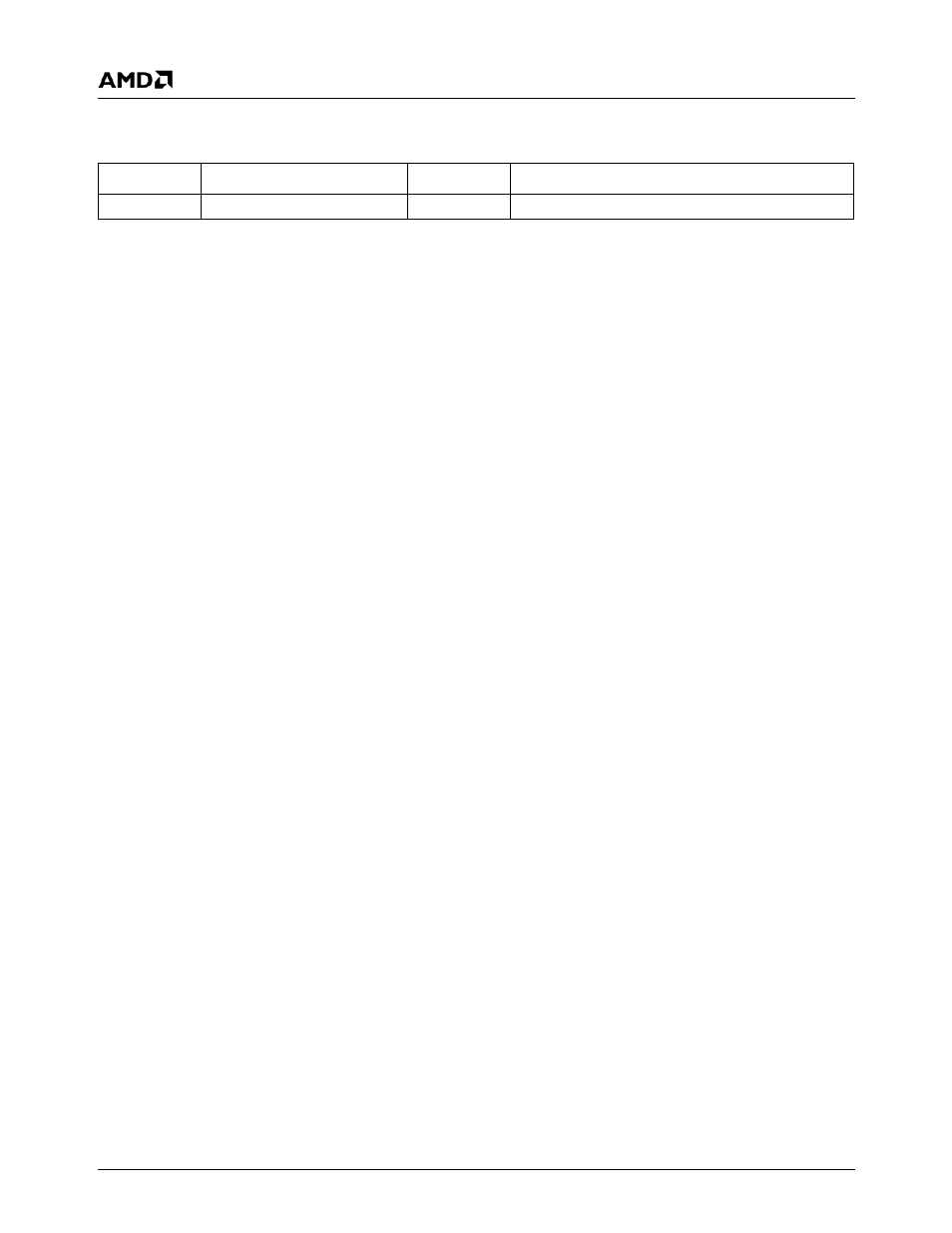

Opcode

Instruction

Clocks

Description

0F 39

DMINT

50-52

Enter DMM and call the DMI handler

IF (CPL<>0 OR (DMM_INST_EN=0 AND SMM=0 AND DMM=0))

#UD;

ELSE

DMM_HEADER[AC_TEMP0] <= AC_TEMP0;

DMM_HEADER[TEMP6] <= TEMP6;

DMM_HEADER[DMM_FLAGS] <= DMM_FLAGS;

DMM_HEADER[EFLAGS] <= EFLAGS;

DMM_HEADER[CR0] <= CR0;

DMM_HEADER[NEXT_IP] <= IP oF INSTRUCTION AFTER DMINT;

DMM_HEADER[CURRENT_IP] <= IP OF DMINT instruction;

DMM_HEADER[CS_LIMIT] <= CS.LIMIT;

DMM_HEADER[CS_BASE] <= CS.BASE;

DMM_HEADER[CS_SELECTOR] <= CS.SELECTOR;

DMM_HEADER[CS_FLAGS] <= CS.FLAGS;

DMM_HEADER[SS_SELECTOR] <= SS.SELECTOR;

DMM_HEADER[SS_FLAGS] <= SS.FLAGS;

DMM_HEADER[XDR7] <= XDR7;

DMM_HEADER[XDR6] <= XDR6;

DMM_HEADER[DR7] <= DR7;

DMM_HEADER[DR6] <= DR6;

if (DMM_CACHE_DISABLE)

CR0 <= 32’h00000010;

else

CR0 <= {1’b0, CR0.CD, CR0.NW, 29’h010};

DR7 <= 32’h00000400;

XDR7 <= 32’H00000000;

SS.flags <= {SS.FLAGS[15:7], 2’b0, SS.FLAGS[4:0]};

CS.FLAGS <= 16’h009a;

CS.SELECTOR <= DMM_BASE >> 4;

CS.BASE <= DMM_BASE;

IF (DMM_LIMIT < 32’g100000)

CS.LIMIT <= DMM_LIMIT;

CS.G <= 1’b0;

else

CS.LIMIT <= DMM_LIMIT | 32’hfff;

CS.G <= 1’b1;

EFLAGS <= 32’h00000002;

DMM <= 1;

Jump to CS at offset of 0;